FIR濾波器的FPGA實現

在時域中,FIR濾波器的輸入/輸出就是一個輸入訊號與單位脈衝相應的卷積。離散方程為y(n)=x(n)*h(n)=∑x(k)h(n-k)=∑h(k)x(n-k),其中y(n)為濾波輸出,x(n)為取樣資料,h(n)為濾波抽頭係數.設計FIR濾波器就是要找到N個係數。N-1階濾波器通常需要N個係數描述,通常需要N個乘法器和N-1個2輸入加法器實現。根據FIR表示式,濾波器實質上就是進行乘累加運算,乘累加的次數由濾波器階數決定。其序列結構如圖

係數表的產生我們利用matlab的FDATool來完成。

首先開啟matlab的FDATool工具,選擇一個38階的帶通濾波,利用窗函式法,視窗型別為kaiser,BETA設定為3.4,通帶頻率為10Hz~20Hz。取樣頻率100Hz。

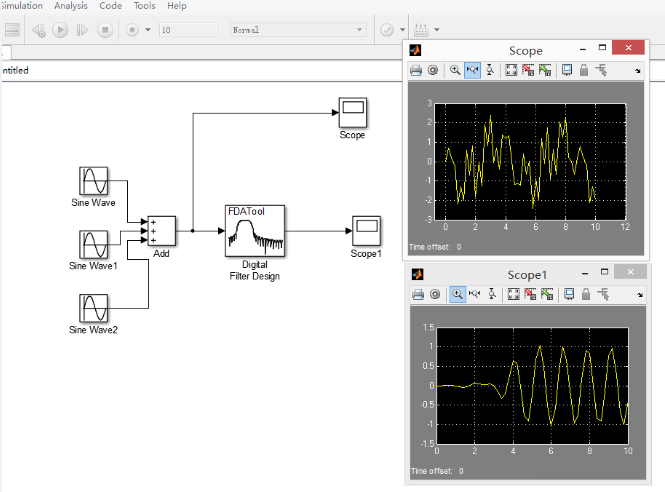

設定好之後點選Design Filter並儲存為.fda檔案。之後在simulation環境下,新增該設計,另外使用y=sin(5t)+sin(15t)+sin(30t)作為輸入訊號,開始執行並檢視濾波器的濾波效果,如下圖

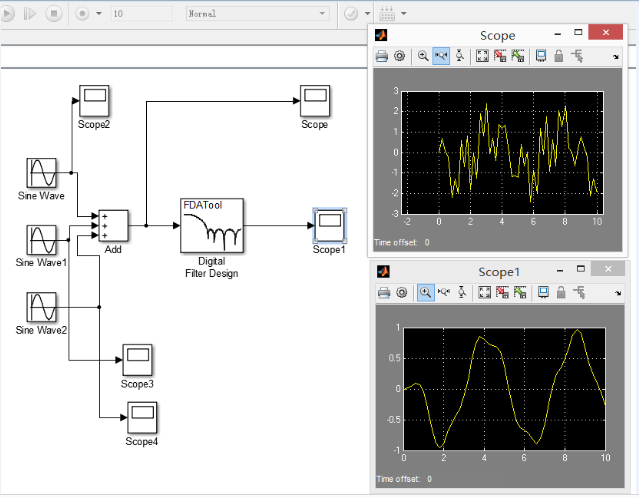

可見這個帶通濾波器的濾波效果還是比較好的,同樣我們可以利用FDATool工具設計一個LowPass Filter,採用等波紋設計法,取樣頻率100Hz,截止頻率為20Hz,同樣用上述的訊號作為輸入,得到如下的濾波效果

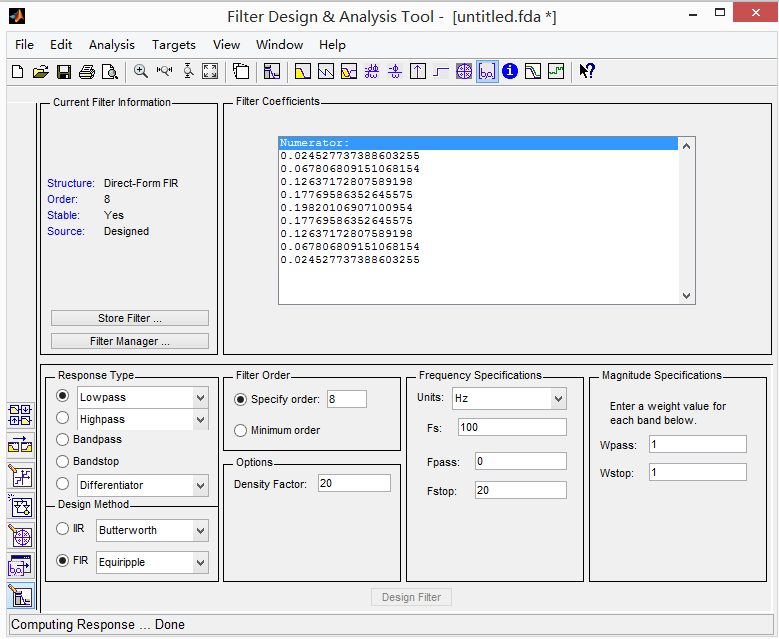

自此我們在matlab中驗證了濾波器的效果,接下來我們需要在FPGA中實現。在我們設定好FDATool的引數後,我們可以點選Analysis-->Filter Coefficients來觀察FIR濾波器的係數,

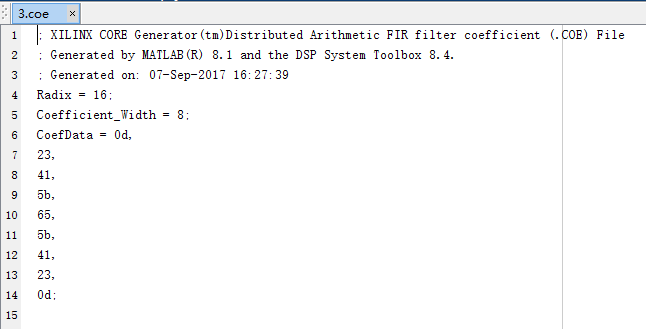

這裡的係數全是有符號型的小數,我們在FPGA中需要用整數作為濾波器的係數,所以我們要進行係數的歸一化,點選左下角設定量化引數(Set Quantization Parameters),Filter arithmetic選擇Fixed-point(定點)。然後就可以匯出Xilink的.coe檔案了。Targets-->XILINK Coefficients(.COE) File.儲存後matlab自動開啟該.coe檔案

CoefData這就是我們FPGA要用的係數表。接下來去編寫Verilog程式碼

module FIR_kaiser_LPF(Clk,Rst_n,data_in,data_out);

parameter word_data_in = 8;

parameter word_data_out = 2*word_data_in+1;

parameter order = 8;

parameter c0 = 8'h0d;

parameter c1 = 8'h23;

parameter c2 = 8'h41;

parameter c3 = 8'h5b;

parameter c4 = 8'h65;

parameter c5 = 8'h5b;

parameter c6 = 8'h41;

parameter c7 = 8'h23;

parameter c8 = 8'h0d;

input Clk;

input Rst_n;

input [word_data_in-1:0]data_in;

output wire [word_data_out-1:0]data_out;

reg [word_data_in-1:0]samples[order-1:0];

reg [word_data_in-1:0]data_in_tmp1;

reg [word_data_in-1:0]data_in_tmp2;

integer i;

相關推薦

濾波器開篇,線性相位FIR濾波器的FPGA實現

可以看到,經濾波器濾波後,頻率為400hz的訊號被保留,時域訊號是完整的正弦波,有些朋友可能會說,怎麼會有失真呢?失真可能是有點,但是還是由於我們的取樣頻率不夠高,都是還原的波形不夠圓滑。還有人可能會說,根據時域取樣定理,不是取樣頻率大於2倍的訊號頻率就可以被還原成原始訊號嗎?但是我們這裡並

FIR數字濾波器的FPGA實現(二)-序列FIR濾波器設計(1)

(二)FIR數字濾波器的FPGA實現-序列FIR濾波器設計 文章目錄 (二)FIR數字濾波器的FPGA實現-序列FIR濾波器設計 0 序列FIR濾波器基本原理 1 基於移位暫存器的序列 FIR 濾波器 1.1 基本理論

直接型FIR濾波器的fpga實現

FIR濾波器根據輸入資料速率的不同可分為序列結構、半並行結構和全並行結構。序列結構的FIR濾波器是將並行資料序列輸入,所需的DSP資源較少,但是資料吞吐率較低;而全並行結構的FIR濾波器資料是並行輸入,濾波係數的個數就決定了所需DSP資源的個數,資源耗用較多,但是吞吐率可

FPGA實現FIR濾波器

1、FIR濾波器總體設計 本設計是基於FPGA實現一個8階的FIR數字低通濾波器。本次設計首先利用MATLAB中的FDAtool工具設計出一個取樣頻率為5KHZ、截止頻率為1KHZ的FIR低通濾波器,通過FDAtool匯出8點係數,然後將係數進行放大、取整,以便於在FPGA

FIR濾波器的FPGA實現

在時域中,FIR濾波器的輸入/輸出就是一個輸入訊號與單位脈衝相應的卷積。離散方程為y(n)=x(n)*h(n)=∑x(k)h(n-k)=∑h(k)x(n-k),其中y(n)為濾波輸出,x(n)為取樣資料,h(n)為濾波抽頭係數.設計FIR濾波器就是要找到N個係數。N-1階濾波器通常需要N個係數描述,通常需

【 FPGA 】SMAC(脈動型乘累加結構)FIR濾波器總結

先貼出來傳統的FIR濾波器實現結構作為後面的對比: 傳統的FIR濾波器的實現結構: (【 FPGA 】FIR濾波器開篇之傳統抽頭延遲線FIR濾波器實現介紹) &nbs

【 FPGA 】FIR濾波器的取樣速率與系統時鐘速率不同時的資源消耗分析

目錄 MATLAB操作 Vivado操作 MATLAB操作 在matlab中命令視窗中輸入:filterDesigner,設計如下引數的帶通濾波器; 在左側第三個功能設定:Set quantization parameters,選擇Filter

Vivado HLS實現FIR濾波器(2)——Vivado呼叫HLS生成的FIR IP核

系統框圖 器件xq7a50tfg484-2I,兩個DDS,輸入時鐘100MHz,輸出分別為8MHz和12MHz,位寬為16位,相乘後輸出位寬32位,三角函式積化和差得4MHz訊號和20MHz訊號,濾波器設計採用Filter Solutions 2015,截止頻率10MHz,取樣率10

Vivado HLS實現FIR濾波器(1)——使用官方C程式碼實現FIR

使用官方C程式碼實現FIR 參考資料: 不同點說明 程式結構 C語言程式碼 模擬綜合 參考資料: 教程——基於HLS實現FIR濾波器https://blog.csdn.net/LZY27

基於HLS實現FIR濾波器--轉載我之前的blog的內容

受人之拖要做個HLS的高階綜合,找了半天,一開始打算做一個FFT,但是一同操作下來,發現難度太大了,回來做一個簡單的硬體的矩陣相乘,發現難度太低,老師不答應做,於是挑了一個FIR濾波器,於是有開始拾起本科時學的濾波器原理,發現好多都忘記了因此接來下就做一個FIR濾波器,下面是我的任

【 FPGA 】FIR 濾波器之濾波器的係數資料(Filter Coefficient Data)

Filter Coefficient Data 濾波器係數使用副檔名為.coe的係數檔案提供給FIR編譯器。 這是一個ASCII文字檔案,帶有單行標題,用於定義用於係數資料的數字表示的基數,後跟係數值本身。 對於N抽頭濾波器,如圖3-36所示。 濾波器係數可以以整數的

【 FPGA 】FIR 濾波器之Single-rate FIR濾波器的係數資料(Filter Coefficient Data)

首先要明確什麼是單速率 FIR 濾波器? The basic FIR filter core is a single-rate (input sample rate = output sample rate) finite impulse response filter.

【 FPGA 】FIR 濾波器之 Half-band Filter 的係數資料(Filter Coefficient Data)

Half-band Filter As previously described, every second filter coefficient for a half-band filter with an odd number of terms is zero. Whe

【 FPGA 】FIR 濾波器之 Hilbert Transform 的係數資料(Filter Coefficient Data)

Hilbert Transform The impulse response for a 10-term approximation to a Hilbert transformer is show

【 FPGA 】FIR 濾波器之 Interpolated Filter 的係數資料(Filter Coefficient Data)

Interpolated Filter A previous section explained that an IFIR filter is similar to a conventional FIR, but with the unit delay operator

【 FPGA 】FIR濾波器之 多個係數集問題以及 使用非整數實數的係數規範問題

多個係數集 對於多係數過濾器,單個.coe檔案用於指定係數集。 每個係數集應附加到前一組係數。 例如,如果設計了一個2係數集,10抽頭對稱濾波器, 係數集#0為:coefdata = -1,-2,-3,4,5,5,4,-3,-2 ,-1; 和係數集#1是: coef

CIC濾波器和FPGA實現

CIC濾波器 CIC濾波器是用不同抽樣頻率進行數字訊號處理的一種FIR濾波器。主要用於數字訊號的抽取和內插。 CIC濾波器由一對或多對積分-梳狀濾波器組成,在抽取CIC中,輸入訊號依次經過積分、降取樣,以及與積分環節數目相同的梳狀濾波器。在內插CIC中,輸入訊號

FIR濾波器實現全通特性的充要條件——理論推導

對於FIR數字濾波器,可設其系統函式為 (1)H(z)=∑n=0N−1anz−n H(z)=\sum_{n=0}^{N-1} a_n z^{-n} \quad \tag{1} H(z)=n=0∑N−1anz−n(1) 從(1)式中,可以看出,H(z)H(z)

教程——基於HLS實現FIR濾波器

注:本博文所需工程下載連結:http://download.csdn.net/detail/lzy272942518/8863107 1.FIR濾波器簡介 FIR(Finite Impulse Response)濾波器:有限長單位衝激響應濾波器,又稱為非遞迴型濾波器,是數字

FPGA數字訊號處理(五)Vivado FIR IP核實現

該篇是FPGA數字訊號處理的第五篇,選題為DSP系統中極其常用的FIR濾波器。本文將在前三篇的基礎上,繼續介紹在Vivado開發環境下使用Xilinx提供的FIR IP核進行FIR濾波器的設計。 IP核概述 Xilinx的FIR IP核屬於收費I