【 FPGA 】FIR濾波器的取樣速率與系統時鐘速率不同時的資源消耗分析

目錄

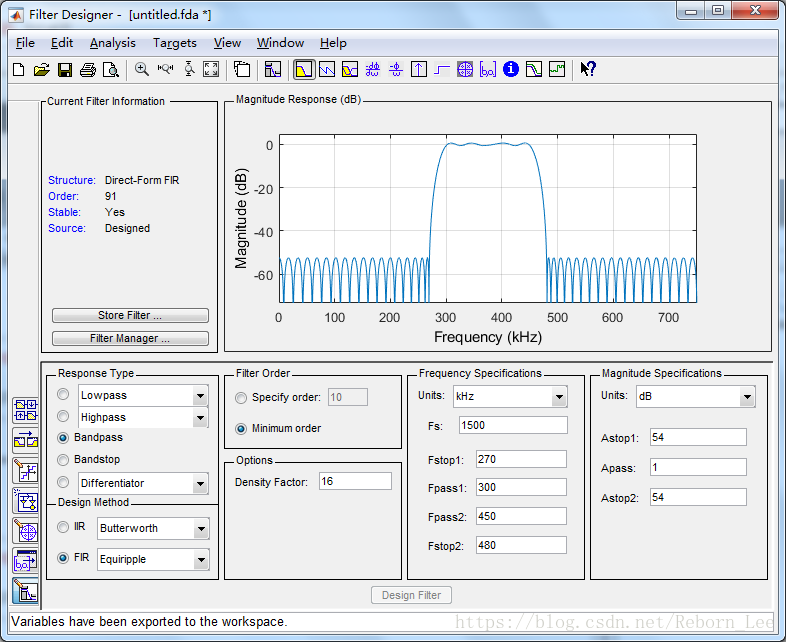

MATLAB操作

在matlab中命令視窗中輸入:filterDesigner,設計如下引數的帶通濾波器;

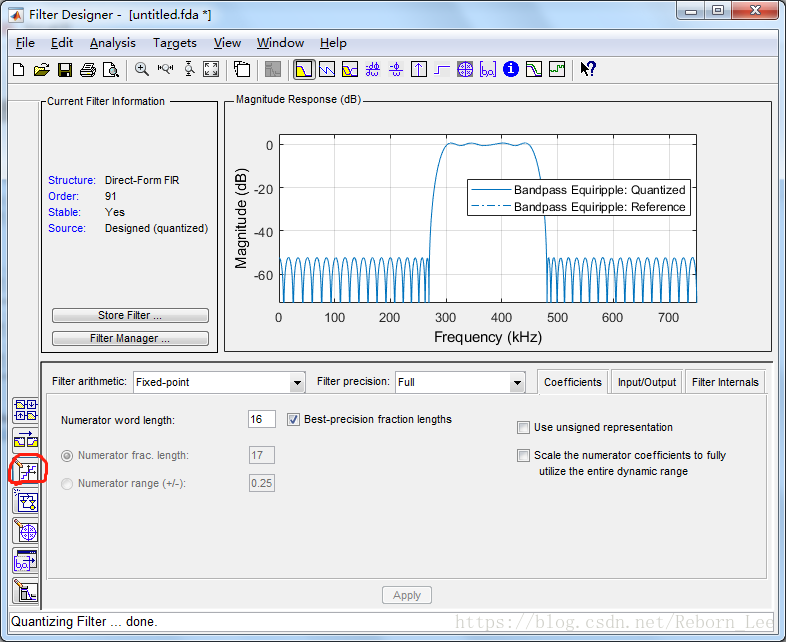

在左側第三個功能設定:Set quantization parameters,選擇Filter arithmetic為Fixed-point,由於只是測試,引數保持預設即可。

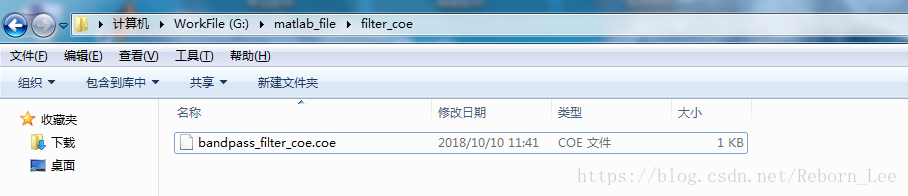

在選單欄中選擇targets,展開選擇生成Xilinx的coe檔案:(自己選擇路徑,命名)

Vivado操作

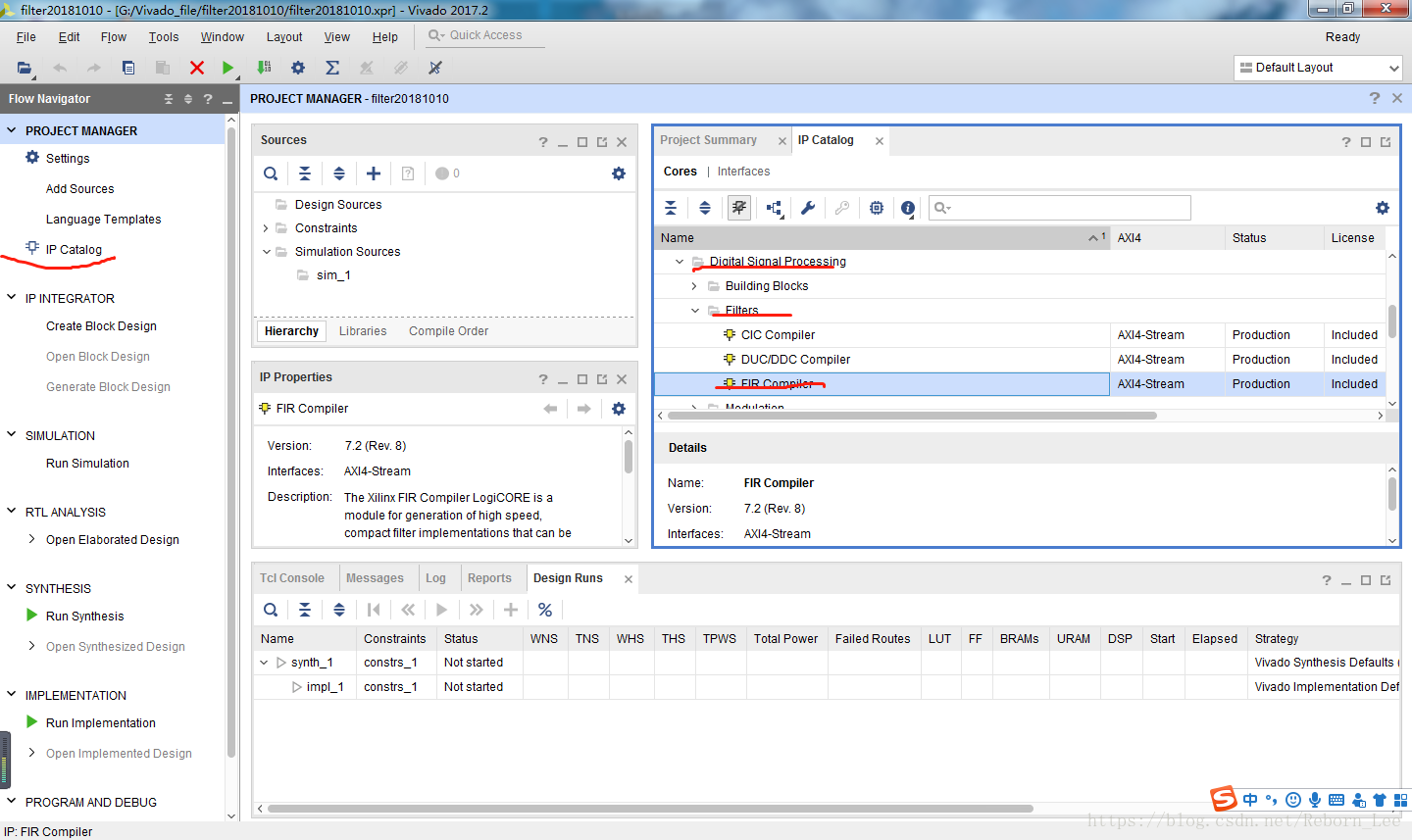

需要設計的FIR的係數檔案搞定了,下面進入Vivado進行IP核設計:

簡單的建立一個Vivado工程,這些都無關緊要,隨便建立一個工程,然後按照下圖的方式建立一個IP核:

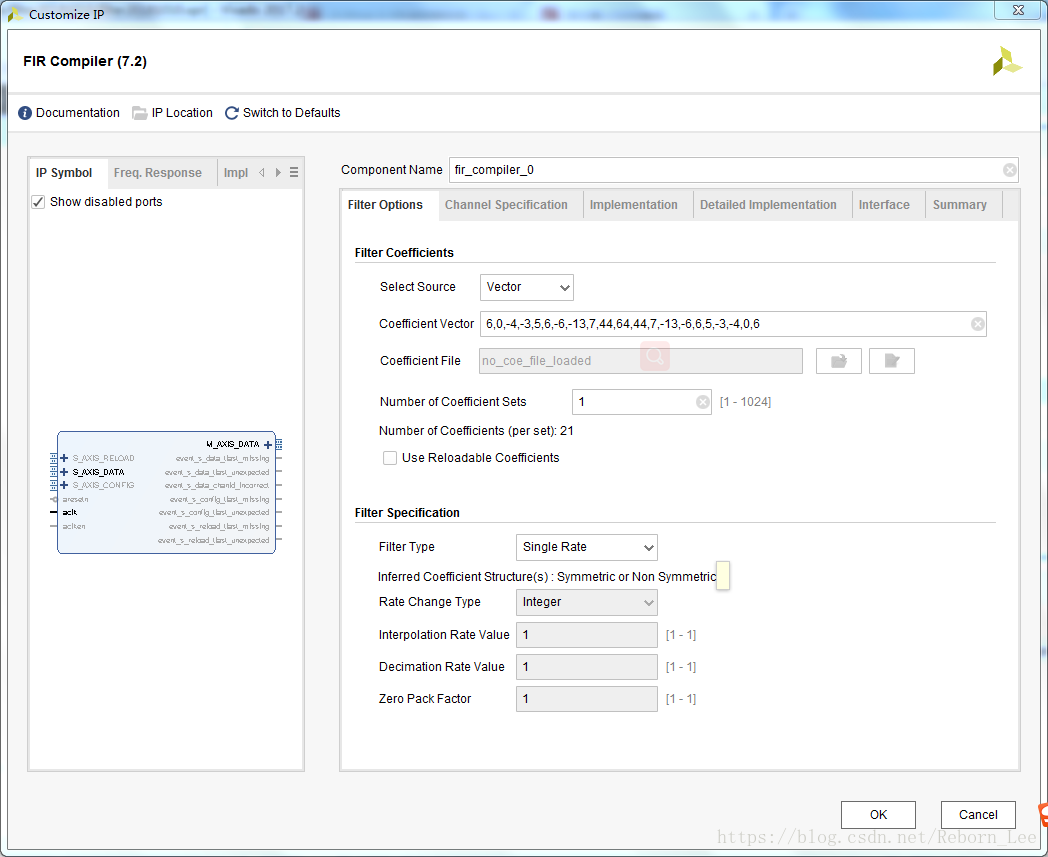

雙擊FIR compiler,進入初始頁面如下:

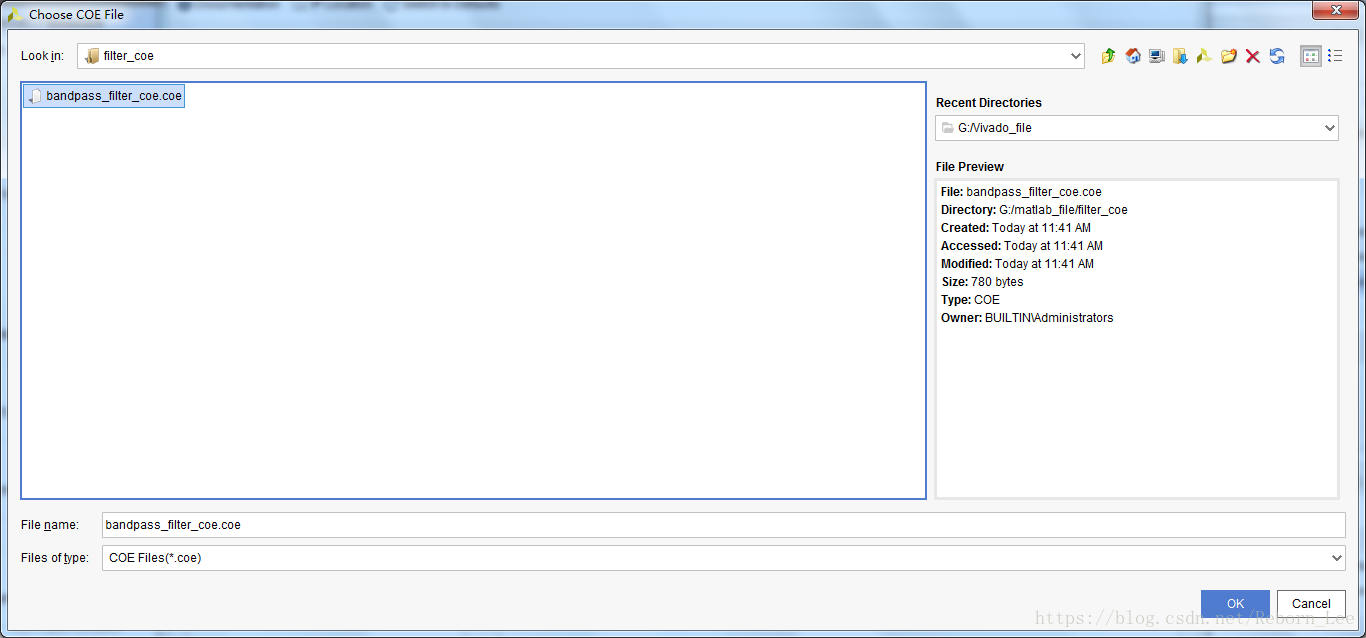

在濾波器係數(Filter Coefficients)下面選擇(select sources)為COE File,然後新增你的coe檔案,也就是上面用matlab生成的係數檔案,載入進去:

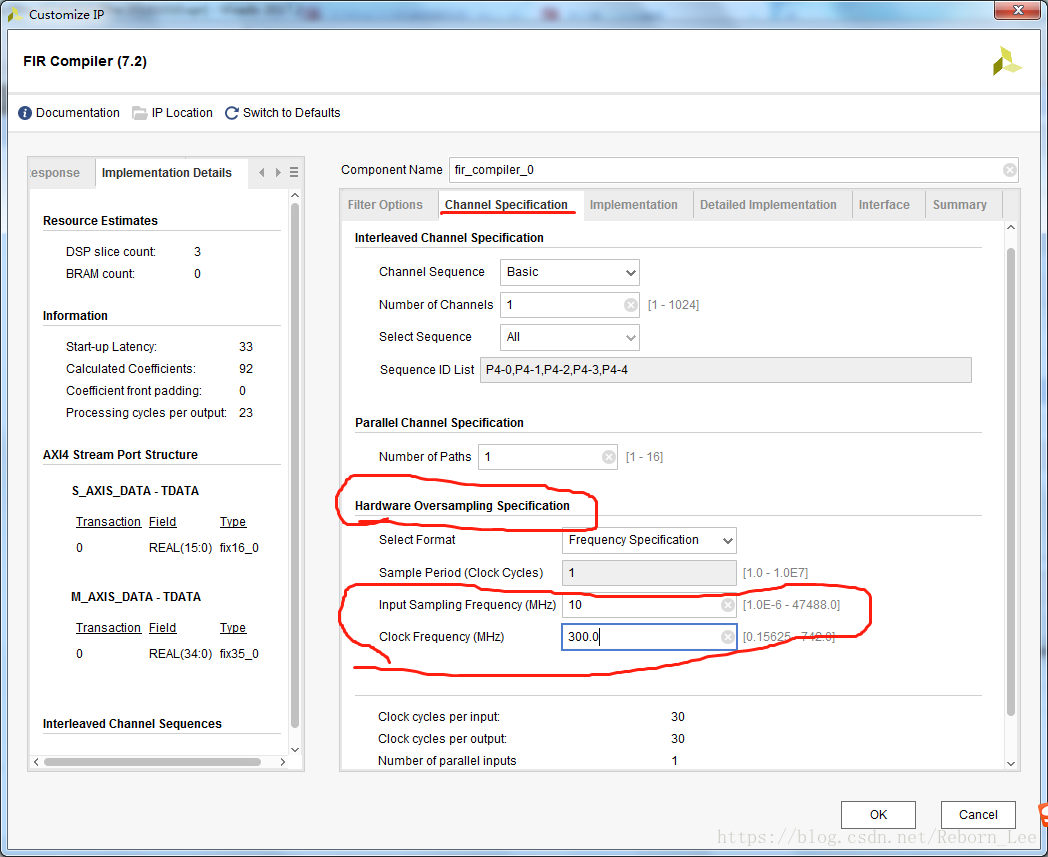

之後,其他基本不需要改,當然到具體的設計中,可以根據需求自己改,這裡改下采樣速率以及時鐘頻率等:

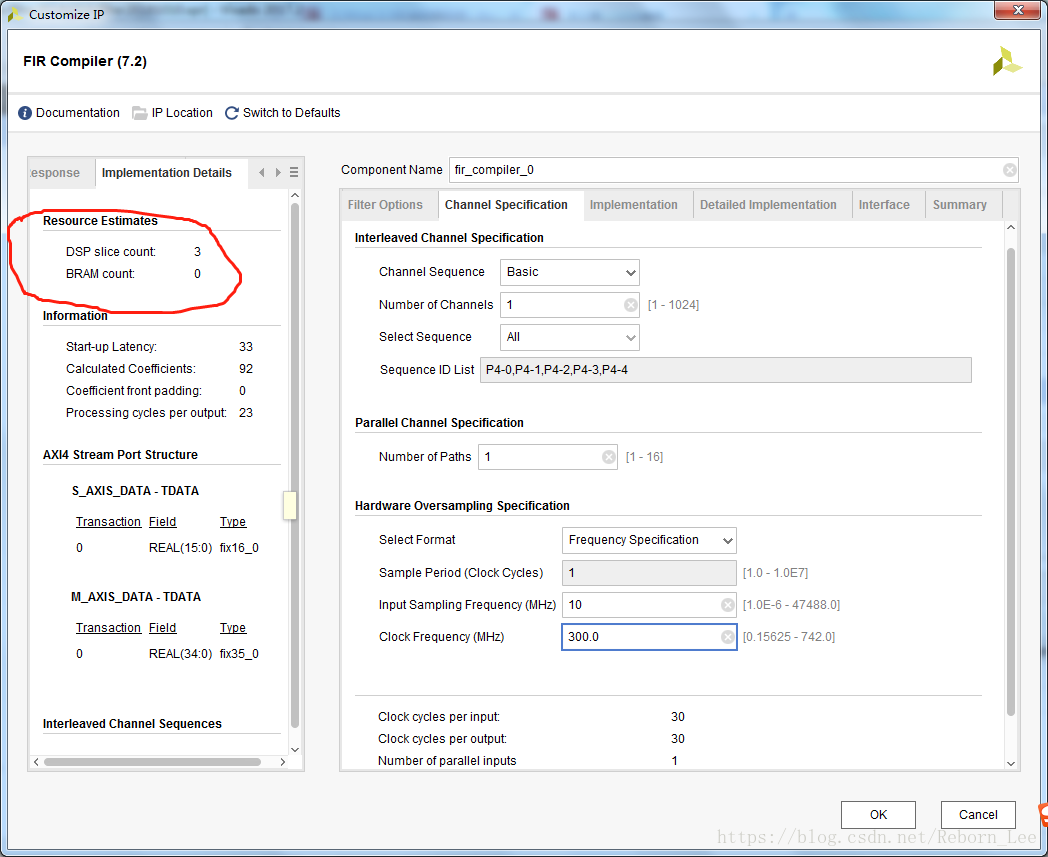

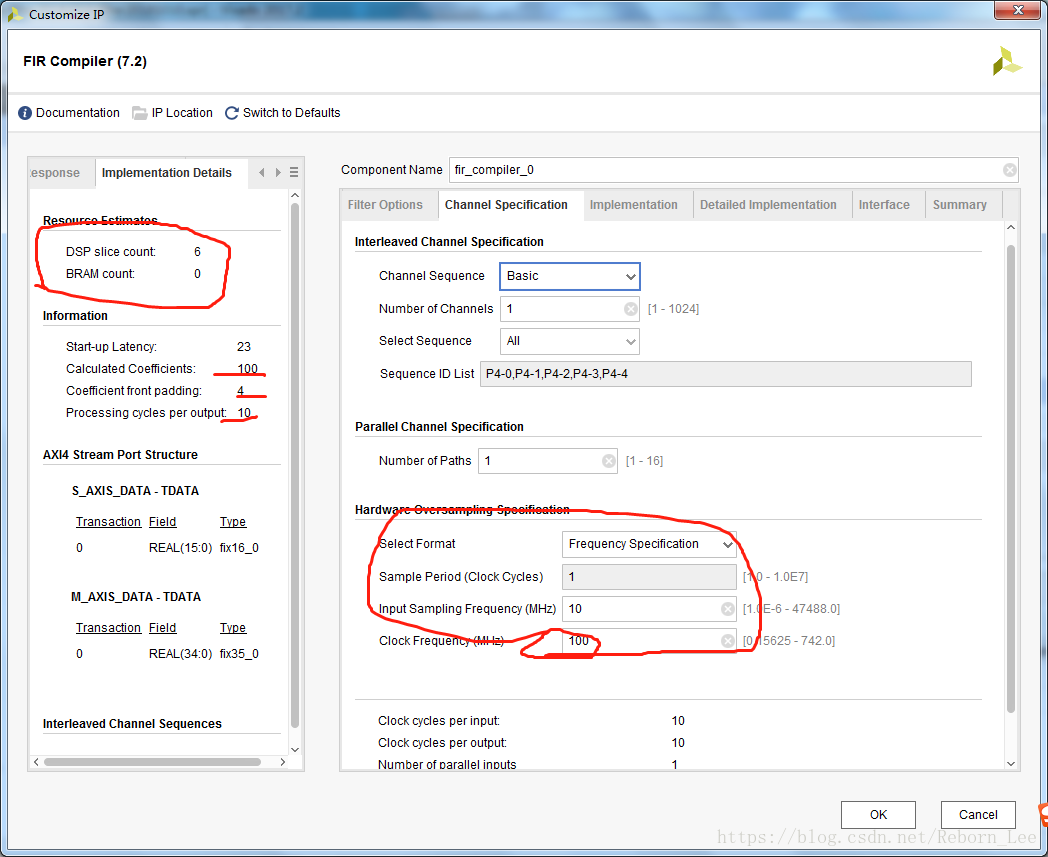

然後我們看下消耗的資源情況:(輸入時鐘為10MHz,時鐘週期為300MHz的情況)

改變下時鐘速率為100MHz,取樣速率不變的情況:

可見,消耗的資源:dsp slice竟然多了!

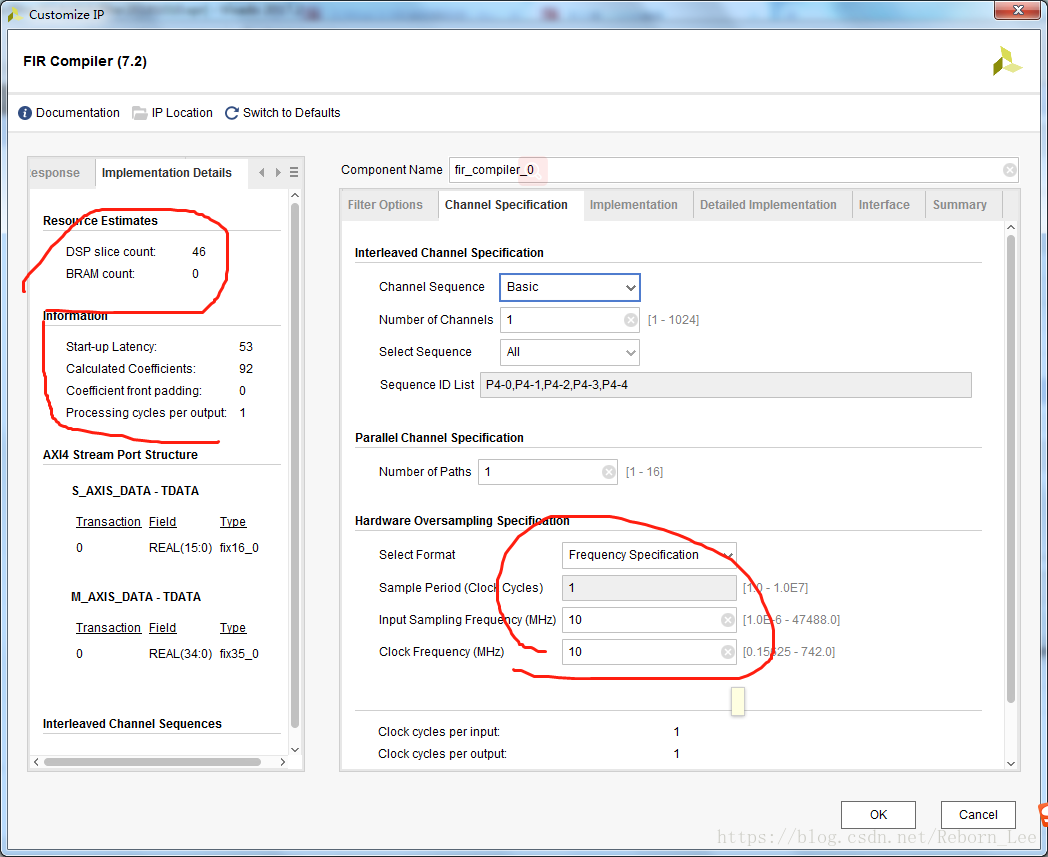

再試:這次改為取樣速率不變,時鐘速率為10MHz,和取樣速率一致,結果如下:

可見,消耗的資源更多了。

這裡我們可以得出初步的結論了,那就是如果系統時鐘速率降低,那麼消耗的資源就越多,反之,時鐘速率增高,那麼消耗的資源就越少。

我們在這裡在提出一個問題,為什麼消耗的資源是DSP slice資源?

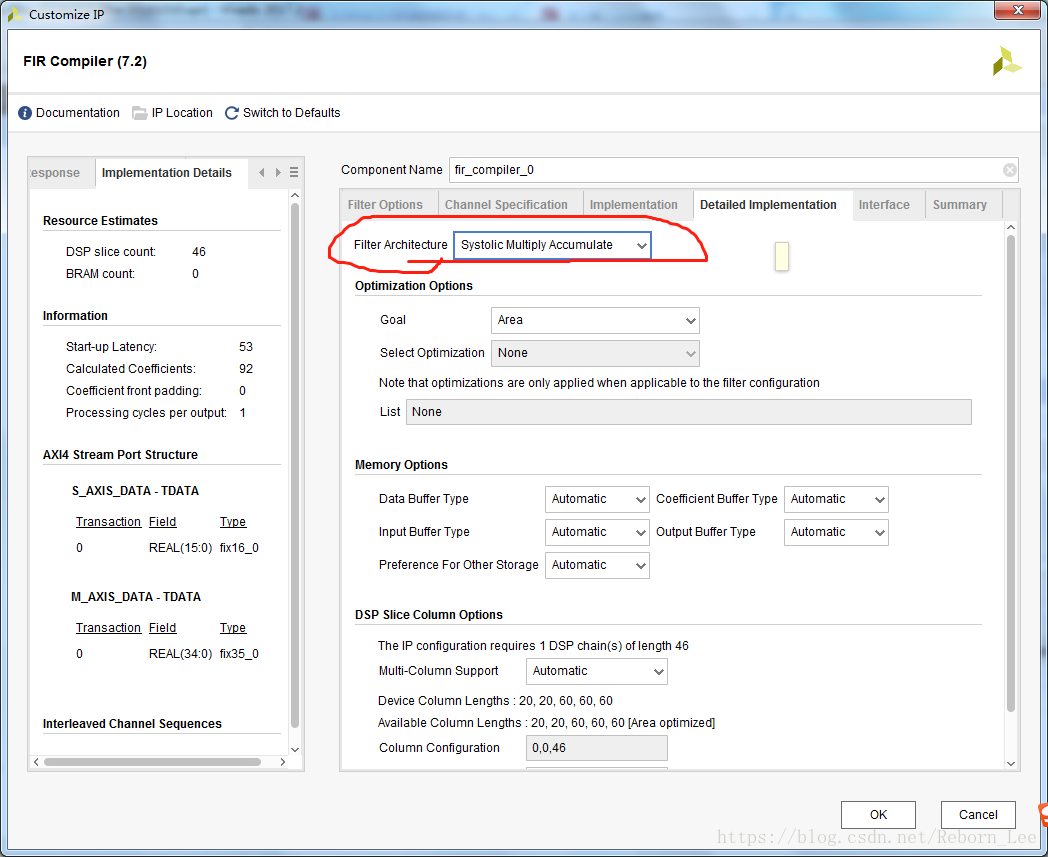

由於使用的SMAC架構:

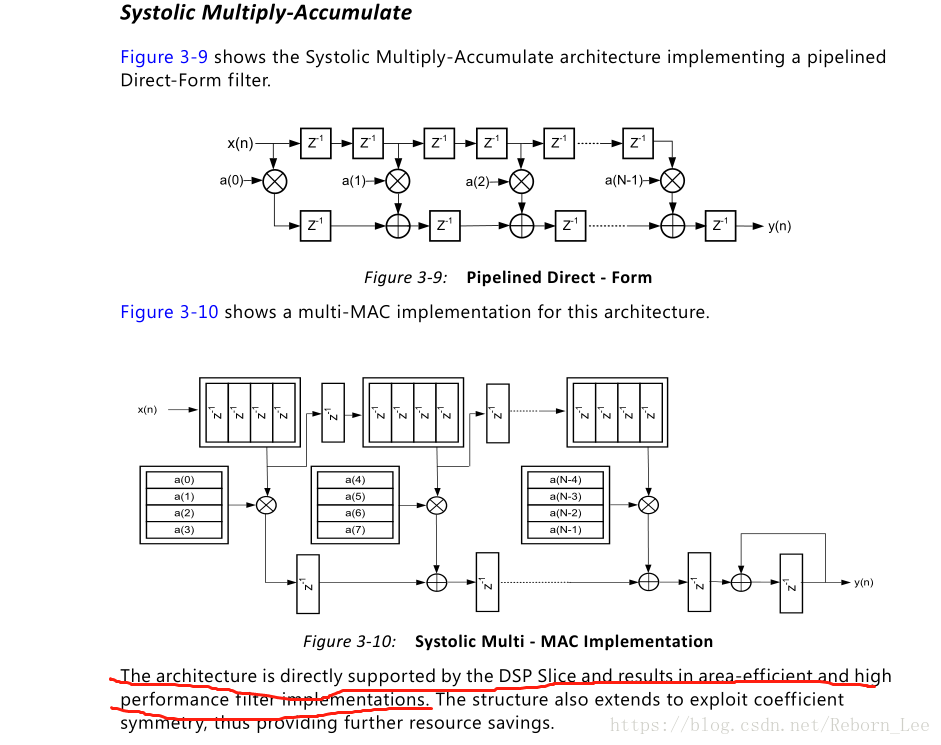

查詢資料手冊有如下這句話:

該體系結構直接由DSP片支援,從而實現了區域高效和高效能的過濾器實現。該結構還擴充套件到利用係數對稱,從而進一步節省資源。

原文如下:

也可以見我的博文:【 FPGA 】FIR 濾波器的架構

暫時記錄到這裡,下篇博文分析下SMAC結構到底是怎麼工作的?