Allegro學習之PCB SI後模擬流程

一、 Cadence Allegro PCB SI簡介.......................................................................................3

(一) 高速PCB設計流程..........................................................................................................................................

二、 Allegro PCB SI的後模擬..................................................................................................4

(一) 準備模擬模型和其他需求..............................................................................................................................4

1. 獲取所使用元器件的模擬模型.....................................................................................................................

(1) 通過官網,供應商等渠道獲取IBIS模型............................................................................................5

(2) IBIS模型轉化為DML模型.................................................................................................................... 5

(3) 通過Allegro建立簡單DML模型以及模型分配.................................................................................

(4) 通過Allegro建立複雜DML模型以及模型分配...............................................................................11

2. 瞭解PCB的佈線規則以及原理圖部分邏輯................................................................................................15

(二) 模擬配置....................................................................................................................................................... 15

1. 使用SI Design Setup配置...................................................................................................................17

2. 選擇需要配置的訊號線...............................................................................................................................17

3. 設定模擬庫...................................................................................................................................................20

4. 設定電源和地網路.......................................................................................................................................22

5. 設定疊層.......................................................................................................................................................27

6. 設定元器件類別...........................................................................................................................................30

7. 為元器件分配和建立模型...........................................................................................................................31

8. 設定差分對...................................................................................................................................................35

9. 設定模擬引數...............................................................................................................................................35

10. SI Design Audit相關........................................................................................................................ 44

11. 提取拓撲.................................................................................................................................................... 46

(三) 後模擬報告結果驗證................................................................................................................................... 50

1. 訊號波形.......................................................................................................................................................50

2. 反射報告,延時報告以及同步噪聲報告...................................................................................................52

一、Cadence Allegro PCB SI簡介

Allegro PCB SI是Cadence SPB系列EDA工具之一,針對電路板級的訊號完整性和電源完整性提供了一整

套完善、成熟而強大的分析和模擬方案,並且和Cadence SPB的其他工具一起,實現了從後端到後端、約束驅

動的高速PCB設計流程。

訊號完整性和電源完整性的模擬按照在這個設計流程中所處的階段可以分為後模擬和後模擬,本文會介紹

Allegro PCB SI在後模擬階段基本的設計流程和操作步驟,並重點介紹其中的配置和模擬專案操作環節。

後模擬是在PCB佈線完成以後,對已經完成的關鍵網路進行模擬驗證的過程。可以檢查實際的物理執行過

程(佈局佈線)是否違背設計意圖;過程。可以檢查實際的物理執行過程(佈局佈線)是否違背設計意圖;或

是已知的改動,通過模擬來驗證這種改動給高速設計帶來的影響。

(一)高速PCB設計流程

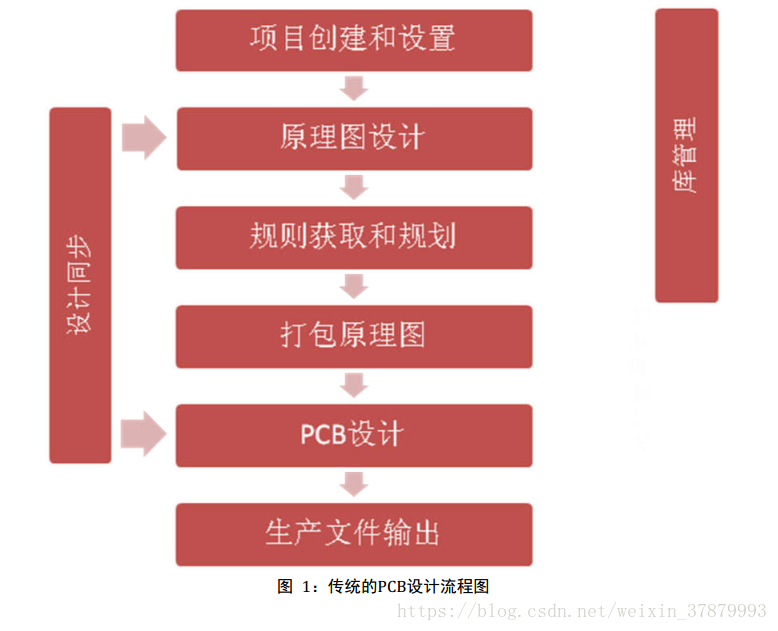

傳統的PCB設計流程如下圖所示:

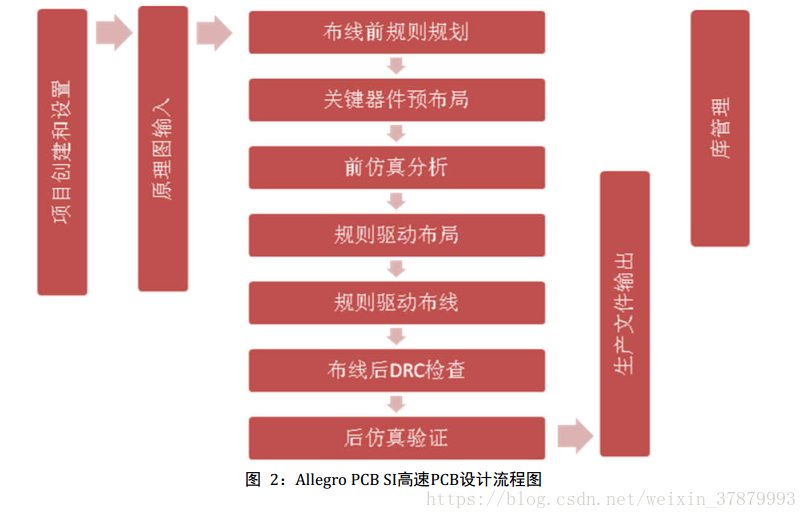

而引入的Allegro PCB SI模擬工具後的設計流程改進為:

二、Allegro PCB SI的後模擬

後模擬,顧名思義,後模擬是在PCB佈線完成以後,對已經完成的關鍵網路進行模擬驗證的過程。可以檢

查實際的物理執行過程(佈局佈線)是否違背設計意圖;過程。可以檢查實際的物理執行過程(佈局佈線)是

否違背設計意圖;或是已知的改動,通過模擬來驗證這種改動給高速設計帶來的影響。

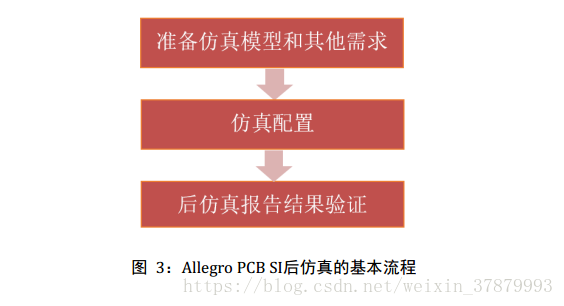

使用Allegro PCB SI進行後模擬的基本流程如下:

(一)準備模擬模型和其他需求

在本階段,我們需要為使用Allegro PCB SI進行後模擬做如下準備工作:

下面,我們會以一個實際的電路板為例,介紹後模擬在Allegro PCB SI 16.6中的具體執行過程。

案例電路板:TX2P_P0_20171225,對其HDMI的差分訊號進行延時以及反射分析。

1. 獲取所使用元器件的模擬模型

(1)通過官網,供應商等渠道獲取IBIS模型

https://www.maximintegrated.com/cn/design/tools/modeling-simulation/ibis/index.cfm

http://www.analog.com/cn/design-center/simulation-models/ibis-models.html

(2)IBIS模型轉化為DML模型

訊號完整性模擬大多針對由晶片IO、傳輸線以及可能存在的接外掛和分立元件所構成的訊號網路系統,為

了實現精確的模擬,模擬模型的精確性是首先需要保證的。一般情況下,Allegro PCB SI會執行傳輸線和分立

元件的建模,而晶片IO和聯結器的模型通常會由原廠提供。

當後業內常見的晶片IO模型有兩種格式,IBIS模型和HSPICE模型;常見的聯結器模型也是兩種,SPICE

(HSPICE)模型和S引數模型。Allegro PCB SI支援包括上述四種模型在內業界流行的模擬模型,但一般都需要

轉化為Cadence自己的DML(Device Modeling Library)後才能使用。

Allegro PCB SI在模擬時需要將模擬模型都轉變成DML模型格式這一做法,區別於大多數EDA軟體,這種

做法可以說是有利有弊。弊,很明顯,就是多一個額外的步驟,雖然這一步驟非常簡便;利,則是有利於模擬

庫的管理,做到模擬庫和原始模型檔案的隔離,並且在檔案格式轉換的同時也執行了模型的校驗。在大多數情

況下,外部模型格式到Cadence DML模型格式的轉換還是非常方便的,只需要用Cadence SPB系列工具包中

的Model Integrity軟體開啟模型檔案,然後點選轉換到DML即可。

可以有兩種方法處理:

其一,在Model Integrity介面下或Allegro PCB SI介面下將IBIS模型轉換成DML格式,供之後的模擬呼叫;

其二,從Cadence SPB 16.5版本開始,Allegro PCB SI名義上也直接支援IBIS模型,所以可以保留現有的

兩個IBIS檔案不做轉換,然後在之後的模擬中直接呼叫。之所以說是“名義上”,因為事實上Allegro PCB SI

還是執行了轉換,只是這個轉換的過程在分配模型的同時一起執行了,沒有擺在明面上。

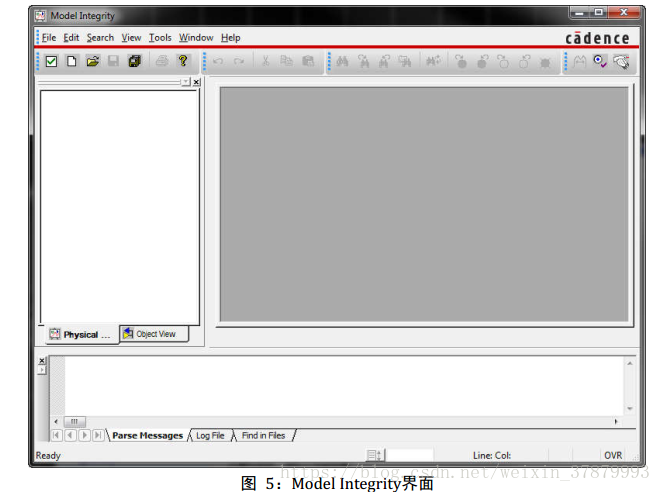

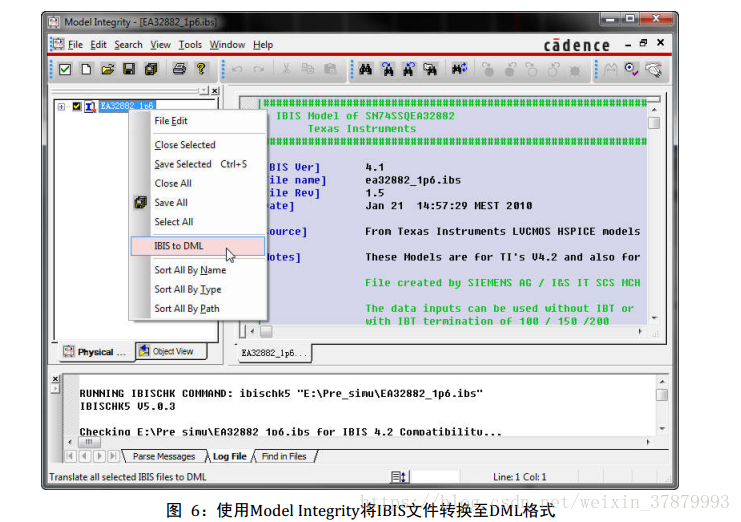

我們先來看看如何使用Model Integrity轉換IBIS模型。

1. 在開始選單找到 Model Integrity快捷方式,或者在目錄%CDSROOT%\tools\pcb\bin(其

中,%CDSROOT%是Cadence SPB的安裝目錄,例如D:\Cadence\SPB_16.6)下找到

modelintegrity.exe執行檔案,點選即開啟Model Integrity視窗。

2. 點選File->Open開啟暫存器的IBIS模型檔案EA32882_1p6.ibs;

3. 右鍵點選瀏覽欄中的EA32882_1p6,選擇IBIS to DML;

(3)通過Allegro建立簡單DML模型以及模型分配

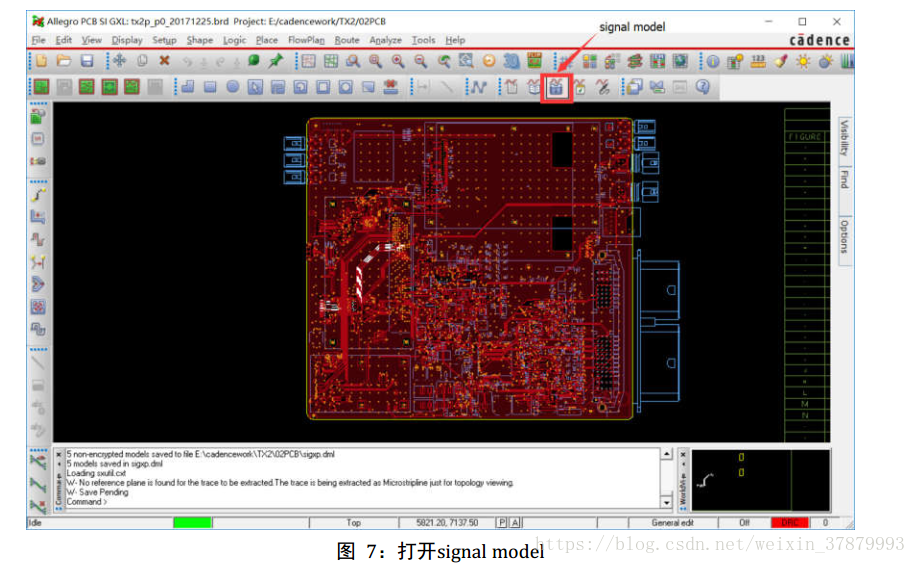

如圖7所示,單擊signal mode:

彈出如下圖8所示:

忽略error,點選OK即可,出現如下圖9所示

Model,出現如下圖10所示:

注意這裡建立的是IBIS模型,選擇create ibisdevice model,單擊OK即可

接著出現如下視窗,圖11:

1:模型名稱,2,3,4:模型pin腳寄生電阻,寄生電感,寄生電容

5:IO內部模型型別 6:IO內部模型,圖中為2.05V,可以更改

7:POWER供電輸入 8:GND

根據datasheet設定好引數後點擊OK即可。如圖12,可以看到U800已經分配剛剛新建的模型

(4)通過Allegro建立複雜DML模型以及模型分配

以上在pin數較少時建IBIS模型方法,如有差分線等複雜情況則如下圖13所示:

點選OK彈出如下圖14所示:

2.瞭解PCB的佈線規則以及原理圖部分邏輯

做模擬分析前,瞭解相關PCB佈線規則,相關電路和介面的原理是必須的。

(二)模擬配置

在本章節中,將會依次介紹如何在Allegro PCB SI介面下進行模型載入和模擬配置,並提取網路拓撲進入

到SigXP介面。模擬配置流程如下

1.使用SI Design Setup配置

無論使用哪一種模擬軟體,在執行模擬以後,一般都需要對電路板進行一定的配置,配置模擬的環境、模

型的分配和引數的設定等等,目的是使模擬能夠按照我們所要求的進行下去。

在Allegro PCB SI 16.6版本中,引入了新的SI Design Setup命令,能夠更有效地引導使用者進行模擬配置。

對於16.3及以後的版本,也存在類似的命令,如Database Setup Advisor。SI Design Setup和Database Setup

Advisor這些命令本身並不是直接的配置命令,它只是一個嚮導,引導使用者一步一步地執行配置,並在每一步上

給出相關配置命令的介面。所以事實上,熟練的工程師也可以不通過這些嚮導直接呼叫相關命令對電路板進行

配置,效果是一樣的。

Allegro PCB SI 16.6版本中的SI Design Setup命令會依次執行以下幾個步驟,我們將會在隨後的章節中介

紹這些步驟的具體執行過程。

2.選擇需要配置的訊號線

為了方便起見,先將之後的所有檔案,包括電路板brd檔案和模擬模型檔案(IBIS和DML)都存放到一個文

件夾中,例如E:\Pre_simu。

在開始選單找到 PCB SI快捷方式,或者在目錄%CDSROOT%\tools\pcb\bin(其中,%CDSROOT%

是Cadence SPB的安裝目錄,例如D:\Cadence\SPB_16.6)下找到allegro.exe執行檔案,點選即開啟Cadence

Product Choices視窗。

選擇Allegro PCB SI GXL,並點選OK按鈕,即開啟Allegro PCB SI視窗。然後通過File->Open開啟

TX2P_P0_20171225.brd檔案。

如果在之後的使用中已經在Cadence Product Choices視窗中勾選了Use as Default的情況下選擇了某個

產品,例如Allegro PCB Designer,可以在Allegro中選擇File->Change Editor,就會彈出Cadence Product

Choices視窗,供重新選擇產品。

在Allegro PCB SI視窗中選擇Setup -> SI Design Setup,會彈出Setup Category Selection視窗。勾選所有

選項,並點選Next進入下一環節。Setup Category Selection視窗會切換Setup Xnet Selection視窗。

| 這裡做一下補充說明,在Setup Category Selection視窗的選項中,除了最下面一項,其它都是我們需要通 |

| 過此嚮導執行的配置專案;而勾選了最後一項“Run Audit upon completion of each setup categoty”則意味著 |

| 我們在之後的每一項配置完成後,點選Next進入到下一環節後,都會自動執行鍼對此環節的模擬稽核,以找出 |

| 我們在配置過程中存在的問題。 |

| 而在Setup Xnet Selection視窗中,我們可以只勾選我們關心的、需要執行模擬和配置的網路,這樣隨後的 |

| SI Design Setup配置嚮導和稽核就只會針對這些勾選網路相關的模型、網路和引數等,不需要花時間在無關的 |

| 網路上。在本案例中,我們勾選Bus HDMI。 |

3.設定模擬庫

接上節,點選Next後Setup Xnet Selection視窗會切換至Setup Library Search Directories視窗,即設定仿

真庫搜尋路徑。預設情況下,庫路徑包括brd檔案所在目錄以及Cadence自帶庫所在目錄,本案例的預設路徑即:

E:\cadenccework\TX2\02PCB

C:/Cadence/SPB_16.6/share/local/pcb/signal

C:/Cadence/SPB_16.6/share/pcb/signal

我們可以通過Setup Library Search Directories視窗右方的按鈕“Add Directory”新增新目錄;在選中某一

原有目錄後,可以用“Remove Directory”按鈕移除;在選中某一原有目錄後,還可以用“Move To Top”、

“Move Up”、“Move Down”和“Move To Bottom”調整目錄的相對位置。這裡需要說明的是,當所有庫路

徑下存在同名模型時,Allegro PCB SI會以最先找到的模型為準,也就是位置靠上的路徑。

當確認了模型庫所在目錄都已正確設定,點選“Next”按鈕繼續。Setup Library Search Directories視窗將

切換至Setup Library File Extensions視窗,即設定模型檔案字尾視窗。一般而言,這裡可保持所有型別的模型

檔案字尾名為預設,直接點選““Next”按鈕繼續。

| Setup Library File Extensions視窗將切換至Setup Working Libraries視窗,即設定工作模型庫視窗。這裡 |

| 會顯示之後所設定的庫路徑下包含的所有DML和IML(Interconnection Model Library)模型庫,其中包括軟體 |

| 自動生成的devices.dml和interconn.iml模型庫(位於brd檔案所在目錄,並且預設成為工作模型庫)。 |

這裡需要說明的是,所有在Allegro PCB SI中新建的模型都會儲存在工作模型庫中,工作模型庫可以叉選

切換,但同時只存在一個。另外,如果需要,我們還可以叉選Ignore Library,選中的模型庫將不會在Allegro PCB

SI中呼叫。

在本案例中,我們保持Setup Working Libraries視窗為預設不變,直接點選“Next”按鈕進入到下一環節。

4.設定電源和地網路

接上節,Setup Working Libraries視窗會切換至Setup Power and Ground Nets視窗,即設定電源和地網路

視窗。Allegro PCB SI會在視窗中顯示已經辨識為電源和地的網路(視窗左方),以及疑似電源和地網路(窗

口右方)。如果網路和原理圖中定義為Power Pin或Ground Pin的管腳相連,則會認為是電源和地網路;如果網

絡雖然沒有和Power Pin或Ground Pin直接相連,但命名中帶有VDD、VTT、VSS等關鍵字串,則會認為是疑

似電源和地網路。

在本案例中,軟體給出的電源和地網路是GND和VCC_3V3_M,VCC_5VM,給出的疑似電源和地網路是

BBAT,HDMI_5V_OUT,VDD_IN_9V_N。我們在左方的Voltage欄中直接輸入電壓值0和3.3V,5V,然後點選

BBAT,選擇下方的Assign Voltage To Selected Net,然後在彈出的視窗中輸入BBAT的電壓值0並OK確認,

HDMI_5V_OUT,VDD_IN_9V_N同上。

點選Setup Power and Ground Nets視窗下方的“Edit Voltage On Any Net In Design”按鈕,會彈出Identify

DC Nets視窗。

在Identify DC Nets視窗中找到需設定的電源和地網路,依次在右方的Voltage欄中輸入電壓值,然後Apply

或OK確認。Allegro PCB SI會彈出警告視窗提示網路與非電源或地管腳相連,不去管它,確認即可。

圖 30:Allegro PCB SI GXL關於電源和地網路的提醒框

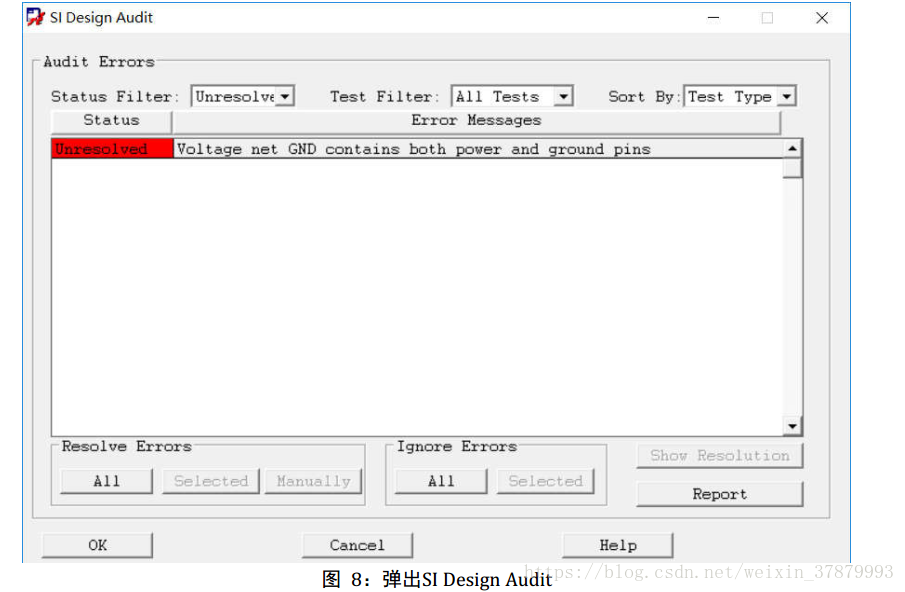

回到Setup Power and Ground Nets視窗,點選“Next”按鈕進入下一環節。不過在本案例中,由於本環

節的設定存在疑似問題,而之後在Setup Category Selection視窗又勾選了最後一項“Run Audit upon

completion of each setup categoty”,因此SI Design Audit視窗會彈出,並顯示此環節存在的疑似問題。

本案例本環節中,疑似的問題是我們在Setup Power and Ground Nets視窗將GND和VDD_IN_9V_N設定

為電源和地網路並賦值,而Allegro PCB SI卻檢查到GND和VDD_IN_9V_N並沒有和任何電源和地管腳直接相

連。由於GND和VDD_IN_9V_N確實是電源,我們可以選擇Ignore Errors忽略它,或者Resolve Errors修復它。

此時,點選Resolve Errors下的“All”按鈕,會彈出Select Errors to be Resolved視窗,視窗中提示所有

VDD_IN_9V_N連線的管腳Pinuse屬性會被修改為POWER,所有GND連線的管腳Pinuse屬性會被修改為GND,

選擇OK確認。

面是自動修復問題。如果希望保持GND和VDD_IN_9V_N電容和匹配電阻管腳的UNSPEC屬性不變,只

把GND和VDD_IN_9V_N相連的金手指管腳屬性修正,可以採用手動地方式執行。選中此錯誤,點選Resolve

Errors下的“Manual”按鈕,會彈出Change Pin Use of a Pin視窗。

| 在Change Pin Use of a Pin視窗中,可以簡單地通過下方的按鈕將所有管腳改為電源或地屬性,也可以點 |

| 擊選中某一管腳後,通過下方的按鈕單獨修改為電源或地屬性。 |

5.設定疊層

接上節,當我們完成針對上一環節的SI Setup Audit並OK確認後,Setup Power and Ground Nets視窗會切

換至Setup Design Cross-Section視窗,即設定疊層視窗。

準確設定電路板的疊層,不僅是模擬的需要,對高速PCB的佈線本身,也有一定的必要,例如Allegro的約

束管理器(Constraint Manager)是支援用傳輸延遲來控制“等長”的,這也是相對於控制傳輸線長度更精確

匹配控制方式,但如果疊層沒有準確設定,傳輸延遲的計算也就不再準確,延遲匹配也就無從談起了。

一般而言,疊層的設計需要依據專案的具體情況,綜合成本、結構、密度、電源、訊號完整性等多方面因

素進行考慮。設計是一個複雜的過程,不過如果是疊層已經確認,只是需要在Allegro PCB SI中輸入,就很簡

單了。疊層的方案可以來自於業界規範,可以來自於已有的設計,也可以來自於PCB板廠的推薦。對於本案例,

是根據PCB板廠的引數來設定的。

在Setup Design Cross-Section視窗中,我們可以點選“Manually Edit Existing Cross-Section”按鈕手動

設定疊層,也可以點選“Load Cross-Section From Another Design”按鈕從現有brd檔案中匯入疊層資訊,或

者點選“Load Cross-Section From A Tech File”按鈕從現有tch檔案中匯入疊層資訊。在此,我們點選“Manually

Edit Existing Cross-Section”按鈕,開啟Layout Cross Section視窗。

我們可以看到這裡的疊層設並不合理,點選底部Refresh Materials按鈕,選擇Refresh All Value,即可。

(Materials的庫如何新增見附件:

materials問題解

決方法.docx

選中錯誤訊息後點擊Resolve Errors欄下方的“ALL”按鈕,然後OK確認進入下一環節。

6.設定元器件類別

接上節,當我們完成針對上一環節的SI Setup Audit並OK確認後,Setup Design Cross-Section視窗會切換

至Setup Component Classes視窗,即設定元器件類別視窗。

器件模型也有幫助。一般而言,規範的原理圖已經對元器件進行了正確的分類,這裡只需要確認一下即可,並

不需要做多少改正。本案例中,我們可以維持預設不變,也可以本著更嚴謹的態度,將金手指(指的是PCB與

其它裝置如主機板、機箱等相連線的電連線插腳,因在其銅箔鍍鎳層上再鍍上了薄薄的一層金,英文“bonding

finger”)從原先的IC類別改為IO類別。然後點選“Next”按鈕進入到下一環節。

7.為元器件分配和建立模型

接上節,當所相關的分立元件中包含沒有正確賦值的(或者說Value值不符合Allegro要求的)元件時,Setup

Component Classes視窗會切換至Assign Values to Discrete Components視窗,即設定分立元件值視窗。如果

都已賦值,則直接進入Assign Models to Components視窗。

在本案例中,有一個磁珠L1沒有賦值。由於此磁珠位於暫存器晶片的模擬電源輸入電路上,對我們要模擬

的訊號無關,所以可簡單的賦值,例如100nH,或是忽略也可。在Assign Values to Discrete Components視窗

選中L1,點選下方的“Assign Value to Selected Components”按鈕,在彈出的賦值框中輸入“100nH”,並

確認退出。

回到Assign Values to Discrete Components視窗,點選“Next”按鈕後,切換到Assign Models to

Components視窗。

點選Assign Models to Components視窗中“Create Default Models For All Discretes