基於Cadence Virtuoso 設計平臺的單片射頻收發積體電路的設計過程

引言

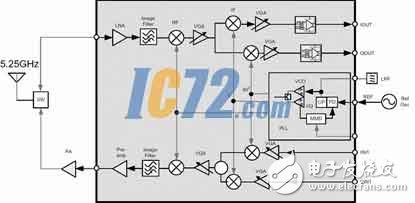

在當前通訊市場的帶動下,通訊技術飛速向前發展,手持無線通訊終端成為其中的熱門應用之一。因此,單片整合的射頻收發系統正受到越來越廣泛的關注。典型的射頻收發系統包括低噪聲放大器(LNA)、混頻器(Mixer)、濾波器、可變增益放大器,以及提供本振所需的頻率綜合器等單元模組,如圖1 所示。對於工作在射頻環境的電路系統,如2.4G 或5G 的WLAN 應用,系統中要包含射頻前端的小訊號噪聲敏感電路、對基帶低頻大訊號有高線性度要求的模組、發射端大電流的PA 模組、鎖相環頻率綜合器中的數字塊,以及非線性特性的VCO等各具特點的電路。眾多的電路單元及其豐富的特點必然要求在這種系統的設計過程中有一個功能豐富且強大的設計平臺。在綜合比較後,本文選定了Cadence Virtuoso 全定製IC 設計工具。

圖1 典型的射頻收發系統

Virtuoso 是Cadence 公司推出的用於模擬/數字混合電路模擬和射頻電路模擬的專業軟體。基於此平臺,Cadence 公司還開發了面向射頻設計的新技術,包括射頻提取技術、針對無線晶片設計的兩個新設計流程。不僅如此,目前的Virtuoso 已經整合了來自合作伙伴安捷倫、CoWare、Helic 和Mathworks 等公司的技術,射頻設計能力大為增強。使用該項新技術,可以減少設計反覆,並縮短產品上市時間。其AMS 工具可以實現自頂向下、數/模混合的電路設計;Composer 工具可以方便地進行電路設計的輸入和管理;Spectre/SpectreRF 模擬器精度高,適合不同特點的電路設計;Layout工具包含了佈局、交叉參考、佈線、版圖驗證、引數提取等功能;此外,Virtuoso能進行可靠的後模擬和成品率控制。

基於Virtuoso 的行為模擬和系統規劃

射頻收發系統的設計最終能否成功,以及模組指標分配是否合理可行,都有賴於具體電路設計之前對系統的行為建模和計算,即所謂的行為模擬。這也是自頂向下設計模式的關鍵一步。Cadence 內建的Verilog-A 和VHDL模擬器,以及混合輸入模式的模擬方法提供了這種可能性。而且,Cadence 軟體免費提供了大量的行為模型供選擇使用,對於射頻系統設計,所要做的就是呼叫並設定各個模組預期的指標要求,通過模擬很快就能得到系統的行為特徵。根據要求可以方便地修改各個模組的指標重新模擬,直到系統的行為滿足要求為止。以接收機為例,接收系統如圖2所示。每個模組的指標設定非常具體,如輸入輸出阻抗、增益、隔離度、噪聲係數NF、線性度IP3、直流偏移IP2等。模擬完成後,每個模組的指標分配任務也同時完成。

每個模組用具體電路實現後可以逐一取代相應的設計模組,進行系統模擬,可以看出每個模組是否滿足系統的需要,進而評估每個實際模組對系統性能的影響。

基於Virtuoso Spectre/SpectreRF 的電路模組

模擬設計

基於上述的行為模擬結果和指標分配結果,可以劃分系統模組設計任務,對每個單元塊分別進行設計模擬。

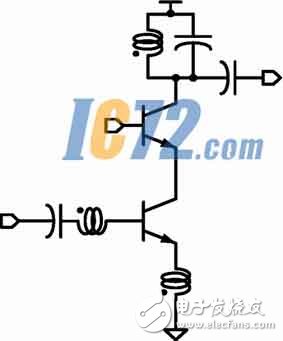

LNA

LNA 是射頻接收機最前端的一個有源部件,它決定了系統的噪聲效能。對它的要求主要是具有儘量低的NF 和足夠的功率增益、好的輸入匹配,其次是高線性度和隔離度。其電路如圖3所示。利用Spectre 的SP 分析或SpectreRF 的PSS+Pnoise 分析都可以進行NF分析。還可以利用NFmin 的結果來挑選電晶體的尺寸,以使最優源阻抗滿足最小的噪聲要求。

圖2 LNA 電路原理圖

Mixer

混頻器是收發機的核心,由於完成的是變頻工作,其主要模擬方法需採用SpectreRF 模擬器。混頻器的增益、NF 等與輸入輸出有關,但輸入和輸出工作在不同的頻段上,往往要在PSS 分析的基礎上進行其它分析才能得到正確結果,如PSP、Pnoise、PAC 等。混頻器的結構是典型雙平衡吉爾伯特。

VGA

基帶VGA 由於頻率低、增益大,因此對噪聲要求不高,主要是對線性度、增益等指標有較高的要求,SpectreRF 的PSS 掃描可以方便地對模組的輸入進行掃描並自動對掃描曲線作延長,直接標示出線性度P1dB 和IIP3 的交點位置及數值大小,非常方便直觀。這種方法與傳統的two tone 測試相比更加靈活高效。VGA 在不同增益狀態下的IIP3 指標的模擬只需把控制寫成變數,在ADE 環境中進行掃描變數的值即可完成。所得的結果可以方便地進行比較分析。通過調整可以獲得理想的VGA 電路。甚至可以把ADE下的各種設定儲存成ocean 的指令碼檔案,利用指令碼的自動執行,只要事先安排好各種模擬任務,Cadence就能自動完成各項模擬並儲存資料結果。對資料進行比較分析後能獲悉電路的效能,以此為指導逐步改進,便可獲得一個滿足系統需要的電路模組。

PLL 模組

PLL 各模組的模擬是一個比較有挑戰性的任務,PLL 本身是一個數字/模擬混合的模組,但是一般都用模擬的方式設計各個模組。PLL 的模擬包含了上百項指標的測試工作,這些模擬要用到幾乎所有Spectre 和SpectreRF 的模擬工具。以其中VCO 和CP 的模擬為例,VCO非線性的工作特點決定了它的噪聲計算不能以小訊號的方式進行,採用PSS+Pnoise的方式則可以準確地模擬VCO 的相位噪聲效能。通過掃描可以得到VCO 的頻率調諧增益Kvco。

電荷泵輸出電流特性是衡量CP 效能的常用曲線,CP 決定了PLL 環路的增益和帶內噪聲效能。通過掃描也可以容易地得到CP 在不同狀態下電流源的恆流和匹配特性。

以上所述是射頻接收機幾個典型單元模組的電路設計模擬過程。系統各個單元塊的模擬是可以同時展開的,完成的模組可以隨時代入行為系統來驗證設計結果。經過若干次反覆修改與驗證,最終可以得到符合要求的接收系統。

溫度分析

要保證最終系統設計的可靠性和成品率,很關鍵的一步是在各個單元塊的設計中進行溫度、極端情況等分析。這些功能可以在Cadence Virtuoso中通過設定不同的模擬溫度、通過模擬模型的Corner 設定,以及直接使用其提供的MonteCarlo 模擬工具來進行。

射頻收發系統的整體電路模擬

各個模組電路分別設計驗證完成以後,就可以把所有模組連成系統,並加上PAD、ESD 等構成一個完整的晶片系統,如圖4所示。對這個系統加上激勵進行模擬測試,如圖5所示,可以對整個系統電路進行模擬。如果模擬計算所用的硬體資源足夠大,可以直接對系統進行tran、SP、PSS,以及PSP、Pnoise、PAC 等分析,獲得整個晶片的效能。如果資源不足,則可以考慮對系統按功能進行分組、分塊模擬。由於分出的塊之間相對獨立,因此整體系統的特性與分塊模擬差別不大。

版圖設計與後模擬

在各模組的設計指標滿足自身及系統要求的基礎上可以開始各個模組的版圖設計,如圖6所示。首先利用Layout-XL 的元件調入功能可以直接由原理圖調入版圖元件,進行各個模組的粗略佈局,主要是安排與其它模組的連線埠以及一些重要元件的預佈局。然後從系統上將所有模組的預佈局調入進行整體佈局考慮。利用Virtuoso Layout 工具所具有的層次化管理和操作的特性,可以對每個模組的安放及其與其它模組的銜接進行系統考慮。

圖3 單片射頻收發晶片版圖設計

系統佈局以後,將邊界條件分配給每個模組。在模組單獨的佈局過程中要遵守其邊界約定。版圖進行到一定階段後,即可以調入到系統版圖中來檢查,隨時作必要的調整以滿足每個模組的具體情況。

具體版圖繪製過程中可以充分利用Virtuoso 版圖工具的強大功能,比如充分發揮快捷鍵功能可以使版圖設計流暢高效;利用Layout-XL 的交叉參考可以隨時發現錯誤的連線或因疏忽造成的短路;利用DRD 的實時規則檢查可以避免絕大多數違反設計規則的布圖。

版圖的規則檢查可以採用Virtuoso 的Diva 工具, DRC、LVS、Extract 等工作都可以在其友好的介面下完成。對於射頻電路版圖元件數規模不大的特點,利用Diva 完成絕大部分工作是很合適的。如果想進一步提高版圖提取和後模擬的精確度,可以考慮採用Assura 工具來進行。

結語

本文詳細討論了基於Cadence Virtuoso 設計平臺的單片射頻收發積體電路的設計過程。討論了利用Virtuoso 工具完成的自頂向下、從系統到模組、從前端都後端的整個設計步驟,直到實現一個完整的射頻晶片。可以看出,Virtuoso 平臺工具在IC 設計的各個階段所發揮的重要作用。

文中所述的單片射頻晶片設計中所採用的Virtuoso工具只是Virtuoso 家族中最常用的幾個工具,依靠他們的強大功能足以完成複雜的射頻系統設計,是價效比較高的一種解決方案。如果再結合Virtuoso 的AMS、UltraSim、VoltageStorm、ElectronStorm等工具,將會使設計效率更高,設計更精確。