Xilinx Zynq-7000嵌入式系統設計與實現 學習教程(1)

學習資料下載地址:http://www.edawiki.com

開篇體會;

Xilinx的ZYNQ系列FPGA是二種看上去對立面的思想的融合,ARM處理器的序列執行+FPGA的並行執行,著力於解決大資料處理、人工智慧等複雜高效能演算法處理。

新的設計工具的推出,vivado HLS,更加註重嵌入式系統的系統級建模,通過HLS工具,使用者只需要編寫C語言程式碼,就可以讓工具自動轉換和生成HDL程式碼

隨著異構架構和片上系統技術的不斷髮展,協同設計、協同模擬和協同除錯將成為未來嵌入式系統開發者必備的素質。所謂的協同,就是要求設計者同時掌握軟體和硬體知識,這與傳統上軟體和硬體分離的設計方法有著本質的區別。

由於半導體技術的不斷髮展,使得電子系統從傳統的PCB板級進化到晶片級,對於嵌入式系統的小型化、低功耗和可靠性的改善都提供了強大的保證。

①全可程式設計片上系統基礎知識

以傳統的現場可程式設計門陣列結構(Field Programmable Gate Array,FPGA)為基礎,將專用的中央處理器單元(Central Processing Uint,CPU)和可程式設計邏輯資源整合在單個晶片中,產生了一種全新的設計平臺,我們稱之為全可程式設計片上系統(ALL Programmable System-on-chip,APSoC).

SoC的架構如下:(固化、靈活性差、專用性強、設計複雜)

APSoC的架構呢??(由詞的全拼意淫,靈活性強,既有固化的又有可靈活控制的。。。)

SoC、CPU、MCU的比較?

SoC:可以整合多個功能強大的處理器核心、可以整合儲存塊、IO資源及其他外設、可以整合GPU\DSP\音訊視訊解碼器等、可以執行不同的作業系統、用於高階應用如智慧手機\平板電腦等

CPU:單個處理器核、需要外部額外的儲存器核外設支援、應用絕大多數場合

MCU:典型的只有一個處理器核心、內部包含了儲存器、IO及其他外設、用於工業控制領域如嵌入式應用

APSoC的誕生背景:

在全可程式設計平臺設計階段,設計已經從傳統上以硬體描述語言HDL為中心的硬體邏輯設計,轉換到以C語言為代表的軟體為中心的功能描述,所以就形成了以C語言描述嵌入式系統結構的功能,而用HDL語言描述硬體的具體實現的設計方法,這也是基於全可程式設計SoC和傳統上基於SoC器件實現嵌入式系統設計的最大區別,即真正實現了軟體和硬體的協同設計。

最大優點可實現硬體加速:

設計者可以根據需求在硬體實現和軟體實現之間進行權衡,使所設計的嵌入式系統滿足最好的價效比要求,例如,在實現一個嵌入式系統設計時,當使用軟體實現演算法成為整個系統性能的瓶頸時,設計人員可以選在在全可程式設計SoC內使用硬體邏輯定製協處理器引擎來高效的實現該演算法,這個使用硬體邏輯實現的協處理器,可以通過AMBA介面與全可程式設計SoC內的ARM Cortex A9嵌入式處理器連線,此外,通過XilinX所提供的最新高階綜合工具HLS,設計者很容易將軟體瓶頸轉換為由硬體處理。

②全可程式設計片上系統中的處理器型別

根據不同的需求,全可程式設計片上系統的處理器可以分為軟核和硬核處理器。

硬核處理器:早期Xilinx將IBM公司的PowerPC硬核整合在V5系列的FPGA中,後來將ARM公司的雙核Cortex-A9硬核整合在ZYNQ 7000系列的SoC晶片中

軟核處理器:對於一些對處理器效能要求不是很高的需求,沒有必要在矽片上專門劃分一定的區域來實現專用的處理器,而是通過使用FPGA晶片內所提供的設計資源,包括LUT\bram、觸發器和互聯資源,實現一個處理器的功能,這就是軟核處理器,對於軟核處理器,他通過HDL語言或者網表進行描述 ,通過通過綜合後才能被使用。

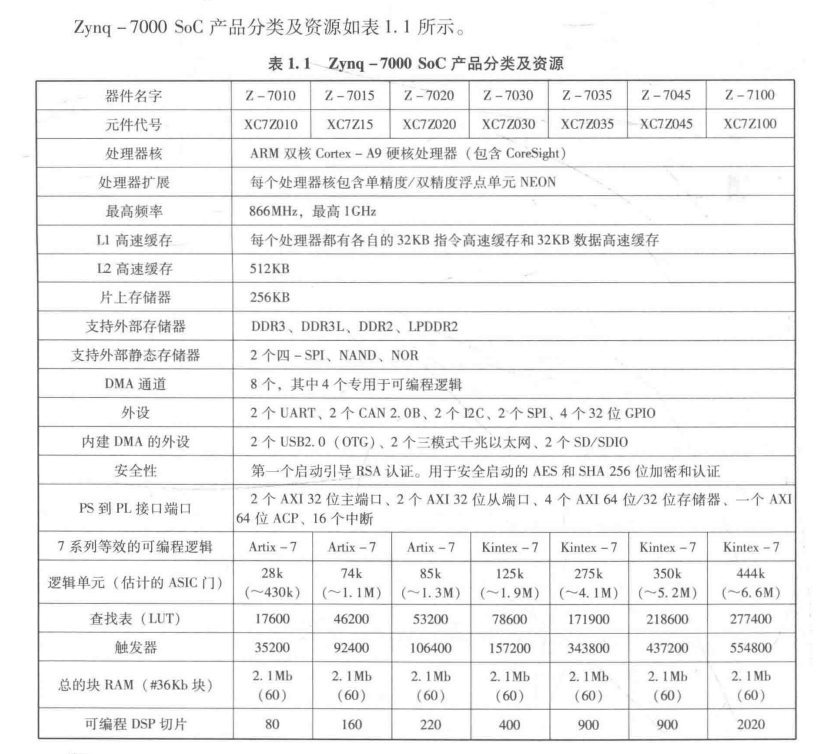

③ZYNQ-7000 SoC功能與結構

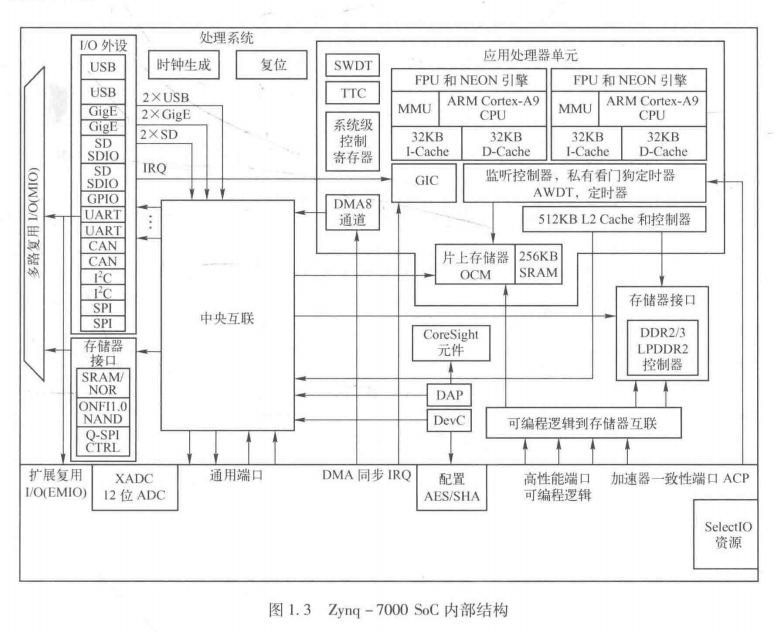

在該全可程式設計SoC中,雙核ARM-Cortex-A9多核CPU是PS的心臟,它包含片上儲存器、外部儲存器介面和豐富功能的外設。

與傳統的FPGA和SoC相比,ZYNQ7000不但提供了FPGA靈活性和可擴充套件性,也提供了專用積體電路的相關效能、功耗和易用性。

ZYNQ 7000的結構便於將定製邏輯和軟體分別對映到PL和PS中,這樣就可實現獨一無二和差異化的系統功能。

與傳統的FPGA方法不同的是,ZYNQ 7000 SoC總是最先啟動PS內的處理器,這樣允許PS上執行的基於軟體程式用於啟動系統並且配置PL,這樣可以將配置PL的國政設定成啟動過程的一部分或者在將來的某個時間再單獨的配置PL,此外可以實現PL的完全重配置或者使用部分可重配置(PR,Partional Reconfihuration,允許動態的重新配置PL中的某一個部分,這樣能夠對設計進行動態的修改)。

-----------------------------------------------------------神聖的分割線-------------------------------------------------------------------------------------------------------------------------------------------------------------

-----------------------------------------------------------休息一下,後續PS構成、PL構成、互聯結構、供電引腳、MIO到EMIO的連結等內容-------------------------------------------------------------------------------------------------------------------------------------------------------------