蜂鳥E203開源RISC-V開發板:蜂鳥FPGA開發板和JTAG偵錯程式介紹

隨著國內第一本RISC-V中文書籍《手把手教你設計CPU——RISC-V處理器篇》正式上市,越來越多的愛好者開始使用開源的蜂鳥E203 RISC-V處理核,很多初學者留言詢問有關RISC-V工具鏈使用的問題。

為了便於初學者能夠快速地學習RISC-V CPU設計和RISC-V嵌入式開發,蜂鳥E203開源MCU原型SoC(在本文中將其簡稱為“MCU SoC”或者“SoC”)定製了基於Xilinx FPGA的專用開發板(在本文中將其簡稱為“FPGA開發板”)和專用JTAG偵錯程式(在本文中將其簡稱為“JTAG偵錯程式”)。

本篇主要就蜂鳥FPGA開發板及蜂鳥JTAG下載器進行詳細說明,更多資訊可下拉頁面到文末,點選“閱讀原文”檢視更多內容。

1 概述

為了便於初學者能夠快速地學習RISC-V CPU設計和RISC-V嵌入式開發,蜂鳥E203開源MCU原型SoC(在本文中將其簡稱為“MCU SoC”或者“SoC”)定製了基於Xilinx FPGA的專用開發板(在本文中將其簡稱為“FPGA開發板”)和專用JTAG偵錯程式(在本文中將其簡稱為“JTAG偵錯程式”)。

完整的FPGA開發板原型(包括FPGA開發板和偵錯程式)如圖1-1所示。

圖1-1 蜂鳥FPGA開發板和JTAG偵錯程式,後文將分別予以詳述。

2 蜂鳥FPGA開發板 概述

2.1 FPGA開發板總體說明

為了便於蜂鳥FPGA開發板的使用,FPGA開發板具備如下特點:

-

一板兩用,該開發板不僅可以用於一塊FPGA開發板作為電路設計使用,同時由於其預燒了蜂鳥E203開源SoC(包括E203核心),因此其可以直接作為一塊MCU SoC原型開發板進行嵌入式軟體開發。即:

-

對於不懂FPGA軟體開發的使用者完全無需做任何的操作,該開發板會預先燒寫開源的蜂鳥E203 Core和配套SoC,上電後即可當做一塊MCU嵌入式開發板來用。

-

對於瞭解FPGA使用的硬體使用者而言,也可以將其當做普通的FPGA 開發板來燒寫普通的Verilog電路以進行FPGA開發。

-

-

由於其預先燒寫的蜂鳥E203 Core和配套SoC原始碼完全開源,可以對其任意進行修改或二次開發。

2.2 FPGA開發板的購買途徑

FPGA開發板的淘寶購買網頁連結:

2.3 FPGA開發板的硬體指標

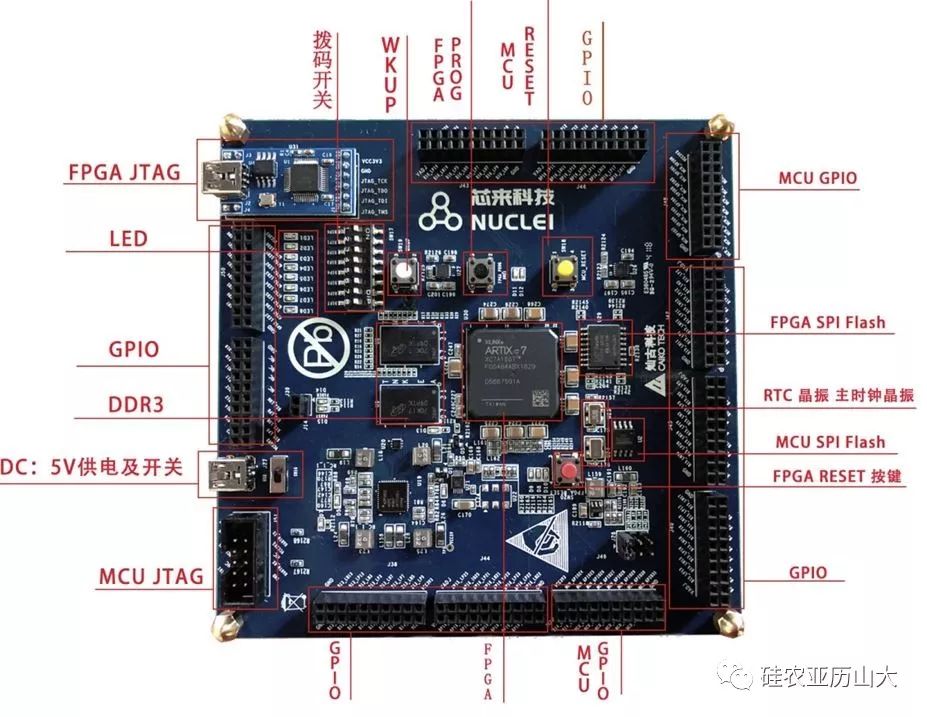

蜂鳥E203專用FPGA開發板是一款入門級Xilinx FPGA開發板,如圖2-1所示。

圖2-1 蜂鳥FPGA開發板總體圖該FPGA開發板的硬體特性如下:

-

使用的FPGA型號為Xilinx XC7A100T。

-

板載雙晶振設計:100MHz主時鐘和32.768K RTC時鐘。

-

配備單獨直流5V供電,並設有電源開關,如圖2-1中的“DC:5V供電及開關”標註。

-

配備獨立的FPGA_RESET按鍵,使用者可用此按鍵作為FPGA的復位按鍵。

-

配備多達126個引出的FPGA GPIO,用於使用者自定義使用。

-

配備多個電源狀態指示LED燈。

-

配備板載的Xilinx Platform Cable USB JTAG下載器,用於對FPGA進行位元流的燒寫,如圖2-1中的“FPGA JTAG”標註。

-

配備兩顆MT41K128M16JT-125K DDR III 顆粒。

-

配備獨立的128M-bit FPGA SPI Flash,此Flash用於儲存mcs格式的位元流檔案:

-

熟悉Vivado和Xilinx FPGA使用的使用者應該瞭解,bitstream檔案燒錄到FPGA中去之後FPGA不能掉電,因為一旦掉電之後FPGA燒錄的內容即丟失,需要重新使用Vivado的Hardware Manager進行燒錄方能使用。為了方便使用者使用,Xilinx的FPGA開發板可以將需要燒錄的內容寫入開發板上的Flash中(以mcs格式),然後在每次FPGA上電之後通過硬體電路自動將需要燒錄的內容從外部的Flash中讀出並燒錄到FPGA之中(該過程非常的快,不影響使用者使用)。由於Flash是非易失性的記憶體,具有掉電後仍可儲存的特性,因此意味著將需要燒錄的內容寫入 Flash後,每次掉電後無需使用Hardware Manager人工重新燒錄(而是硬體電路快速自動完成),即等效於,FPGA上電即可使用。

-

除了上電自動對FPGA重新進行燒錄外,使用者還可以通過強行按FPGA開發板上的“FPGA_PROG”按鍵觸發硬體電路使用此Flash中的內容對FPGA重新進行燒錄。FPGA開發板上的“FPGA_PROG”按鍵位置請參見圖2-1中標註所示。

-

-

為了便於此開發板直接作為MCU原型嵌入式開發板使用,將蜂鳥E203開源SoC的頂層引腳直接連到開發板上,並配有明顯的絲印標註。請參見第2.5節瞭解詳細介紹。

-

為了便於此開發板作為常規FPGA開發板使用,配備分離的撥碼開關和LED燈,請參見第2.6節瞭解詳細介紹。

2.4 FPGA開發板的電路原理圖

該開發板的電路原理圖保存於:

2.5 FPGA開發板的MCU部分

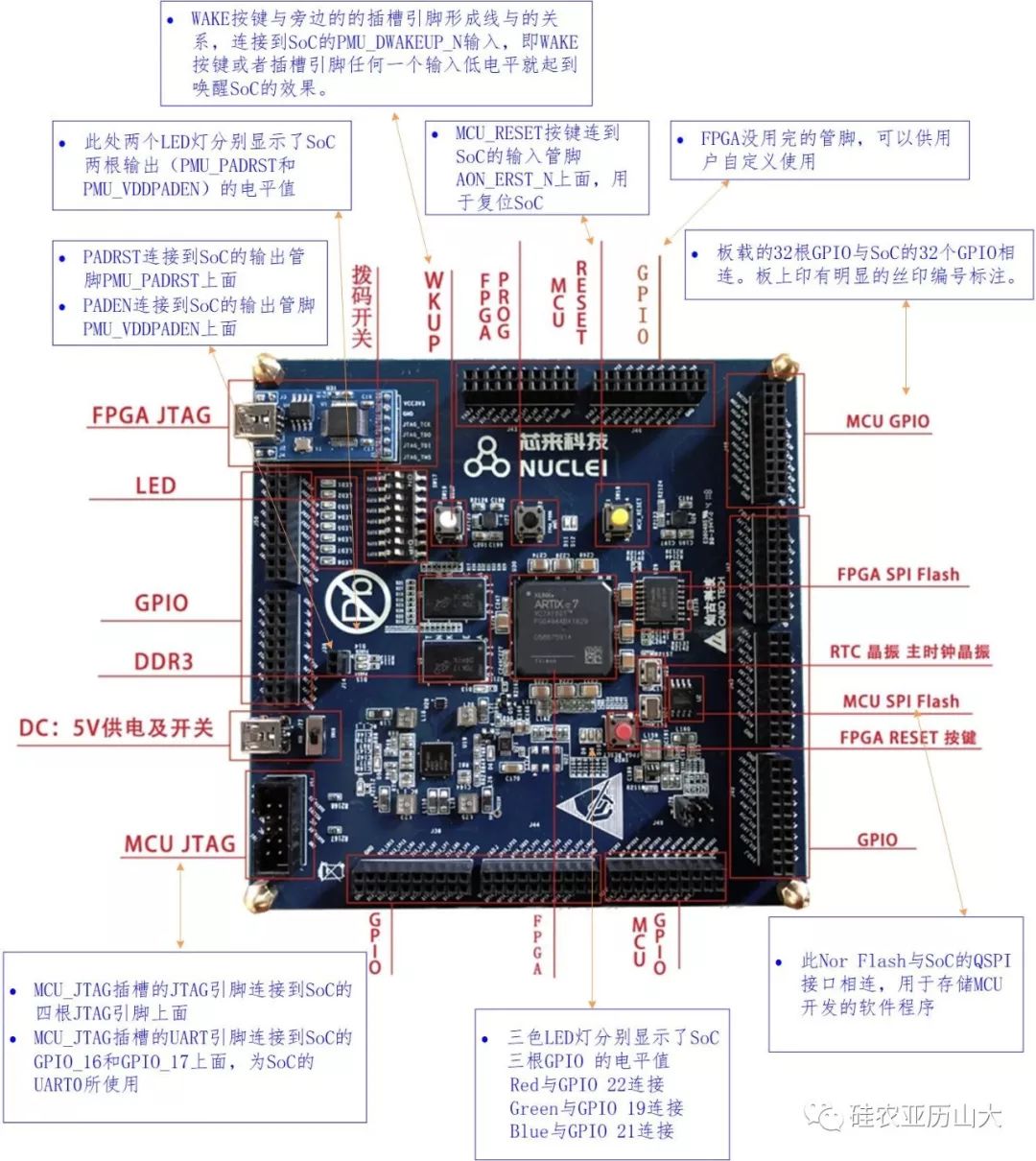

為了便於此開發板直接作為MCU原型嵌入式開發板使用,將“蜂鳥E203開源SoC”(簡稱SoC)的頂層引腳直接連到開發板上,並配有明顯的絲印標註,詳細描述如圖2-2中所示,其要點如下:

-

FPGA預先燒寫成為“蜂鳥E203開源MCU SoC”(簡稱SoC)

-

為了實現MCU的功能,在FPGA開發板上專門配備了一個Nor Flash用於儲存MCU的軟體程式。

-

MCU SoC的兩個輸入時鐘輸入分別按照如下方式產生:

- 低速的實時時鐘直接由FPGA開發板上的32.768KHz時鐘源輸入

- 高速時鐘由FPGA開發板上的100MHz時鐘經過FPGA內部PLL降頻而得(16MHz)。高速時鐘由FPGA開發板上的100MHz時鐘經過FPGA內部PLL降頻而得(16MHz)。

-

將SoC的相關輸入輸出管腳明確的做到FPGA開發板上,並且用印刷字型明確的表明埠號。

-

有關此SoC的輸入輸出管腳列表的詳細資訊,請參見https://github.com/SI-RISCV/e200_opensource/blob/master/doc 目錄下的文件《蜂鳥E203開源SoC簡介》。

-

注意:所有的管腳都只是對映到FPGA內部的普通埠(雙向IO)上,然後通過FPGA Project通過設定埠對映把FPGA埠對映到這些外部預定義的開發板引腳。有關FPGA Project的詳細資訊請參見:https://github.com/SIRISCV/e200_opensource/blob/master/doc 目錄下的文件《蜂鳥E203快速上手介紹》。

-

更多詳細描述如圖2-2中所示。

圖2-2 蜂鳥FPGA開發板的MCU定製部分

2.6 FPGA開發板的常規功能部分

為了便於此開發板作為常規FPGA開發板使用,配備分離的撥碼開關和LED燈,如圖2-3中所示。

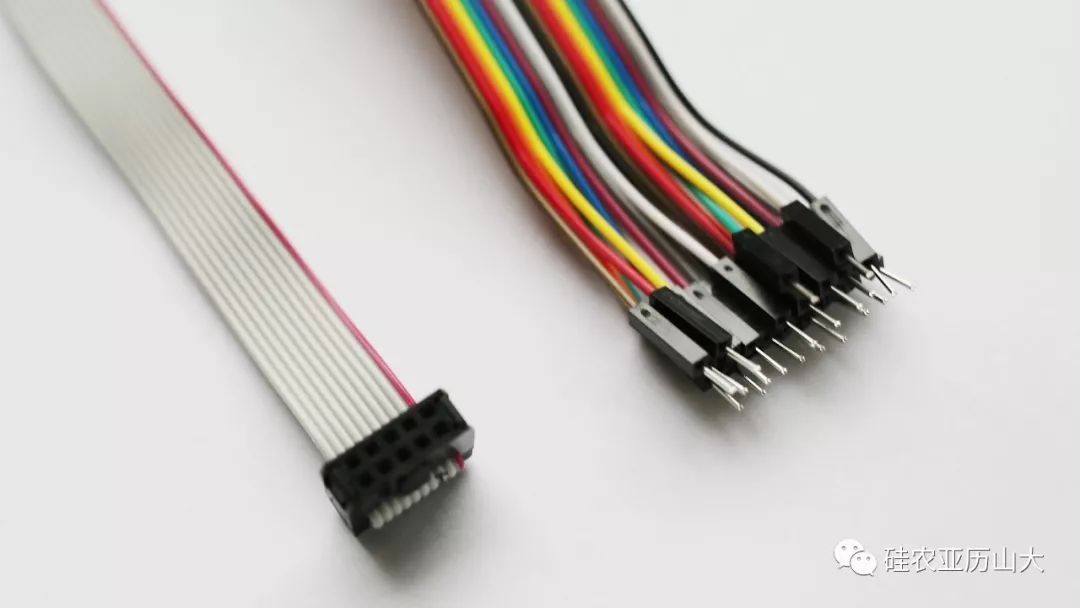

注意:此組撥碼開關和LED並沒有被連線到FPGA的管腳上,使用者可以自由的進行跳線使其控制開發板上的其他訊號。如圖2-3中所示,使用者可以通過用杜邦線跳線將“撥碼開關”與MCU SoC的GPIO介面連線,相當於通過撥碼開關來產生GPIO的輸入,從而可以程式設計構建形象化的簡單Demo。

2.7 燒寫蜂鳥E203專案至FPGA開發板

有關如何燒寫蜂鳥E203專案(包括SoC和處理器核心)至此FPGA開發板的具體操作步驟,請參見https://github.com/SI-RISCV/e200_opensource/blob/master/doc 目錄下的文件《蜂鳥E203快速上手介紹》。

2.8 使用FPGA開發板進行軟體開發與除錯

有關如何使用FPGA開發板進行軟體開發與除錯的具體操作步驟,請參見https://github.com/SI-RISCV/e200_opensource/blob/master/doc 目錄下的文件《蜂鳥E203快速上手介紹》。

3 蜂鳥JTAG偵錯程式

3.1 JTAG偵錯程式總體說明

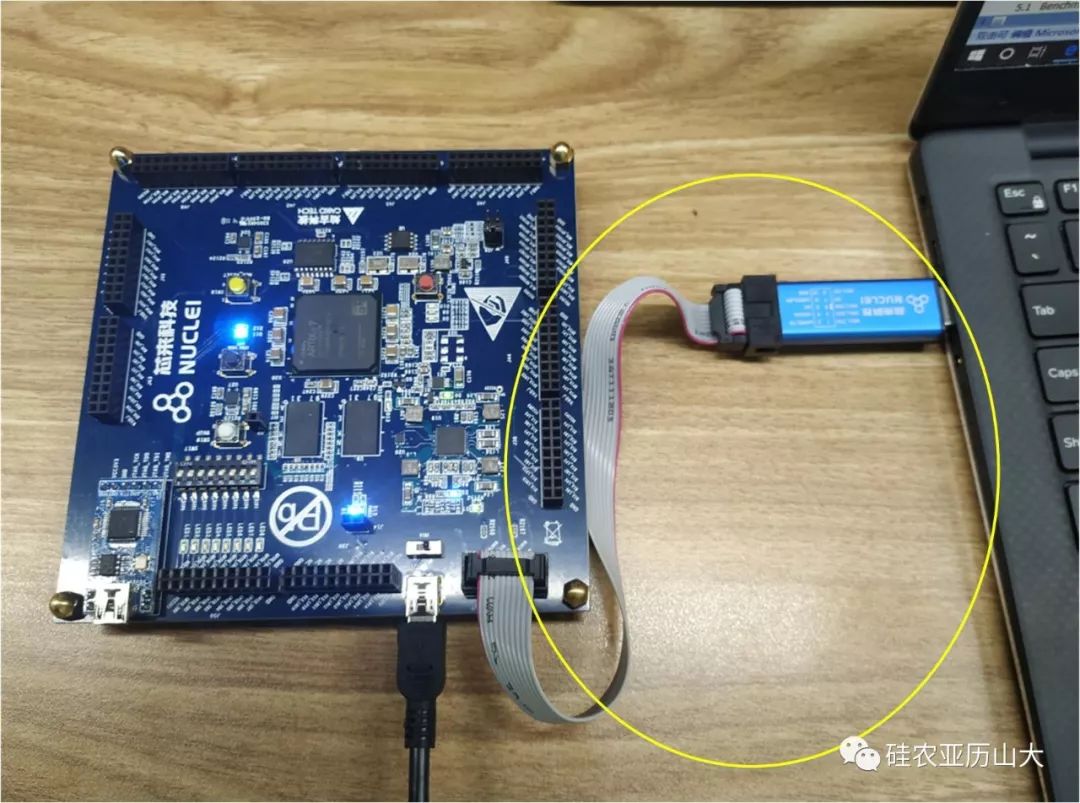

圖3-1 蜂鳥E203專用的JTAG偵錯程式

為了便於初學者能夠快速地學習RISC-V嵌入式開發,“蜂鳥MCU SoC”定製了專用的JTAG偵錯程式,該偵錯程式具有如下特性:

-

偵錯程式的一端為普通U盤介面,便於直接將其插入主機PC的USB介面,另一端為標準的4線JTAG介面和2線UART介面。

-

偵錯程式具備USB轉JTAG功能,通過標準的4線JTAG介面與蜂鳥E203 FPGA開發板連線。由於蜂鳥E203 核心支援標準的JTAG介面,通過此介面可以程式下載或進行互動式除錯。

-

偵錯程式具備UART轉USB功能,通過標準的2線UART介面與蜂鳥E203 FPGA開發板連線。由於嵌入式系統往往沒有配備顯示屏,因此常用UART口連線主機PC的COM口(或者將UART轉換為USB後連線主機PC的USB口)進行除錯,這樣便可以將嵌入式系統中的printf函式重定向列印至主機的顯示屏。參見中文書籍《RISC-V架構與嵌入式開發快速入門》第9章瞭解更多詳情。

3.2 JTAG偵錯程式的購買途徑

FPGA開發板的淘寶購買網頁連結:

3.3 JTAG偵錯程式與FPGA開發板相連

蜂鳥E203的JTAG偵錯程式與FPGA開發板的連線方法如圖3-2中所示。

3.4 使用JTAG偵錯程式進行軟體下載與除錯

有關如何使用JTAG偵錯程式進行軟體下載與除錯的具體操作步驟,請參見https://github.com/SI-RISCV/e200_opensource/blob/master/doc 目錄下的文件《蜂鳥E203快速上手介紹》。

(檢視方式:1.下滑頁面到文章最末,點選“閱讀原文”檢視e200_opensource專案總連結;2.在公眾號後臺回覆“連結”,即可訪問)

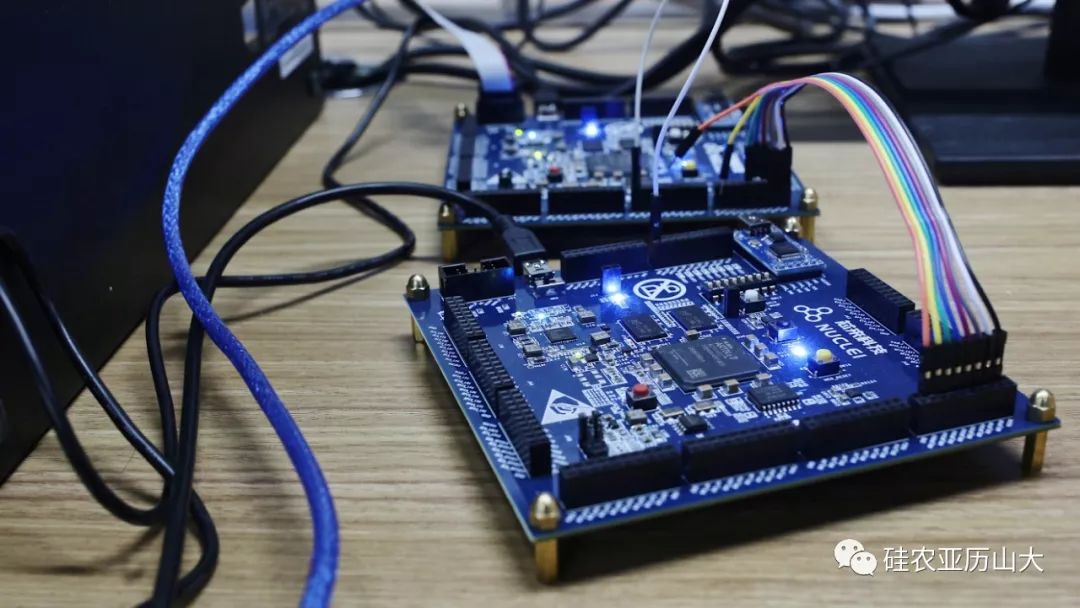

4 購買連結及圖片欣賞

FPGA開發板的淘寶購買網頁連結:

其他

本文編輯by 新晉矽農胖夏

如您有關於此開發板的任何資訊諮詢,請致信[email protected]

更多資訊

感興趣的讀者可以通過下面二維碼關注公眾號“矽農亞歷山大”,瞭解Verilog、IC設計、CPU、RISC-V和人工智慧AI相關的更多設計技巧和經驗分享,注意:由於乾貨太多,請自備茶水。