計算機組成與設計(四)—— 加法和減法的實現

阿新 • • 發佈:2018-11-30

二進位制加法

半加器(Half Adder)

半加器的功能是將兩個1位二進位制數相加。輸入埠A、B,輸出埠S(輸出),C(進位)。

其有一個很明顯的缺點:不能將低位的進位參與運算。

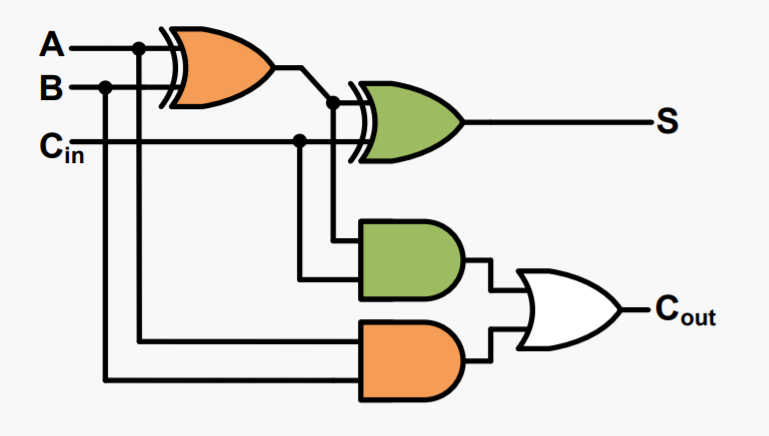

全加器(Full Adder)

全加器由兩個半加器構成。輸入埠A、B、Cin,輸出埠S(和)、Cout(進位輸出)。

有了全加器,只要將它簡單的連在一起就能實現多位的加法器。

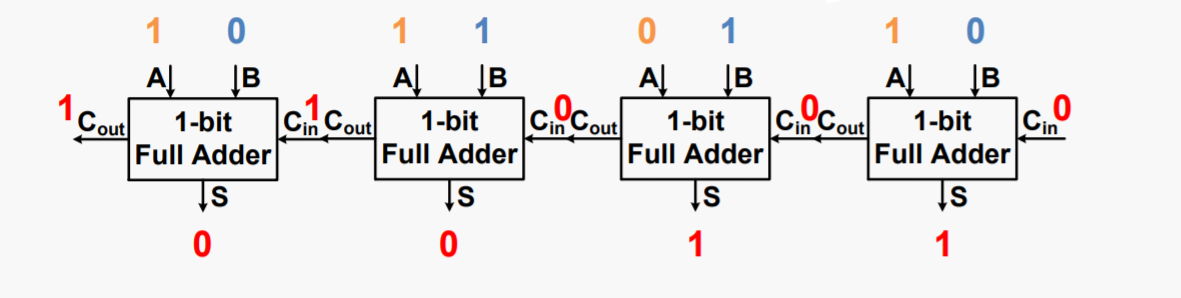

4-bit 加法器

例如求 (1101)2 + (0110)2,答案應該為和為 (0011)2,進位為1.可以用4個全加器構成4-bit全加器來實現,如圖

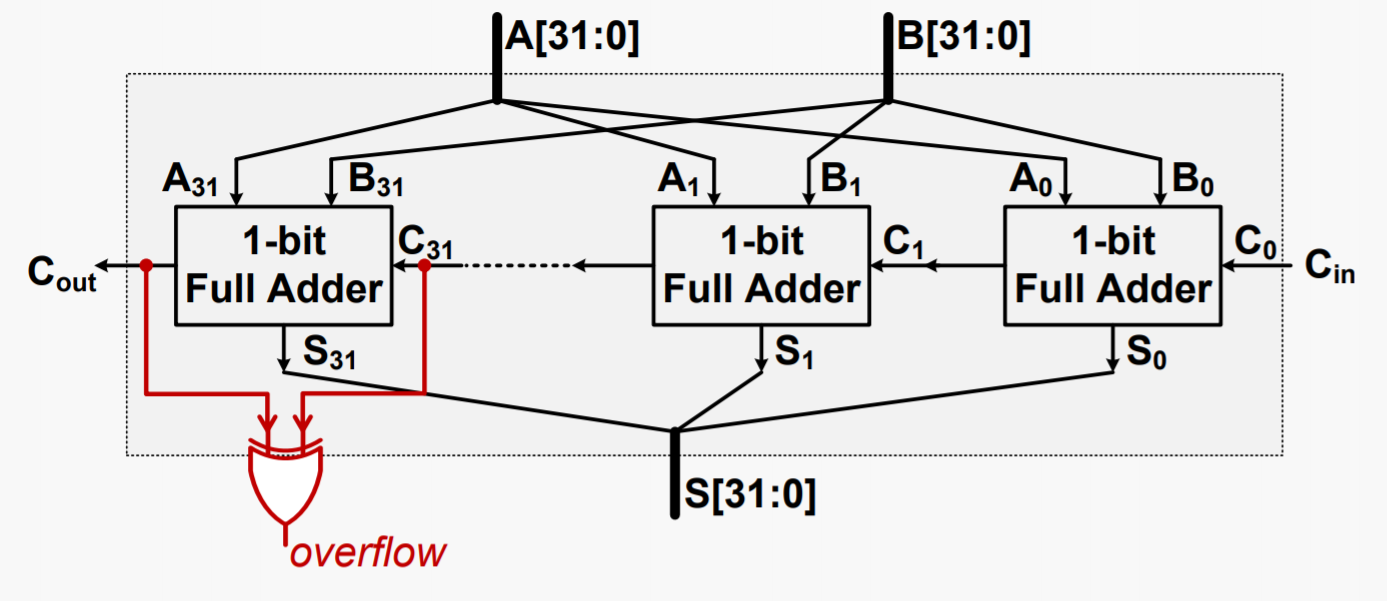

顯而易見,這個圖可以推廣,所以這樣就能得到32-bit的加法器。

溢位

檢查加法結果是否溢位

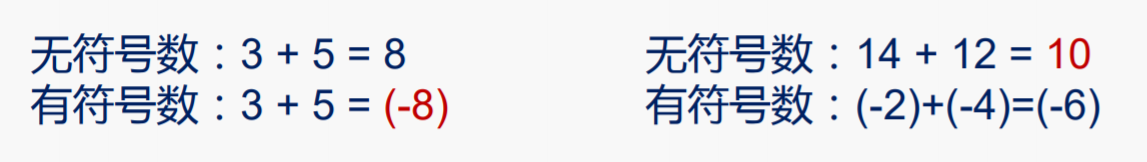

溢位(overflow):是指運算結果超出了正常的表示範圍

- 溢位僅針對有符號運算而言的,發生溢位有兩種情況:兩個正數相加,結果為負數;兩個負數相加,結果為正數。其實,無符號時可看作是mod 2k(k是最大位數),既然取模了,自然不用考慮溢位

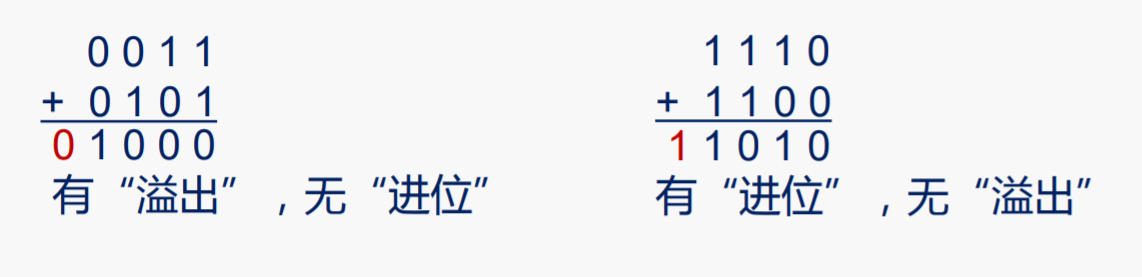

- 有溢位不一定有進位、有進位不一定有溢位

- 有符號加法和無符號加法在運算時硬體電路是一樣的,只是對結果的解讀不同

4-bit運算時

溢位的檢查方法

“最高位的進位輸入”不等於“最高位的進位輸出”,說明產生了溢位。

經過一個異或門,如果C31 和Cout 不相等,overflow被設為1,表示溢位。(為什麼可以通過這種方法判斷呢?)

對溢位的處理方式

MIPS

提供對兩種不同指令分別的處理

- 將運算元看作有符號數,發生“溢位”是產生“異常”,如add rd,rs,rt addi,rt,rs,imm

- 將運算元看作無符號數,不處理“溢位”,如addu rd,rs,rt addiu rt,rs,imm

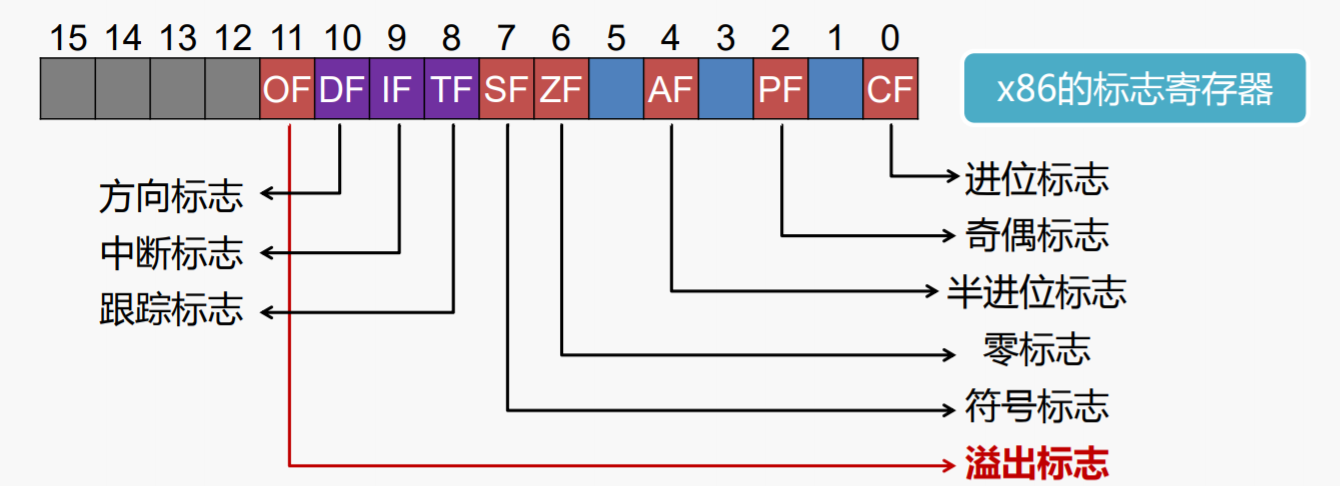

X86

設有“溢位標誌OF”(Overflow Flag)。如果把操作看作有符號數,若發生溢位,則自動設定OF=1;否則OF=0。

二進位制減法

原理

- 減法運算可轉換成加法運算

- 只需將負數變成它的補碼,補碼與原碼之間的轉換規則:按位取反、末位加一

- A - B = A + (~B + 1)

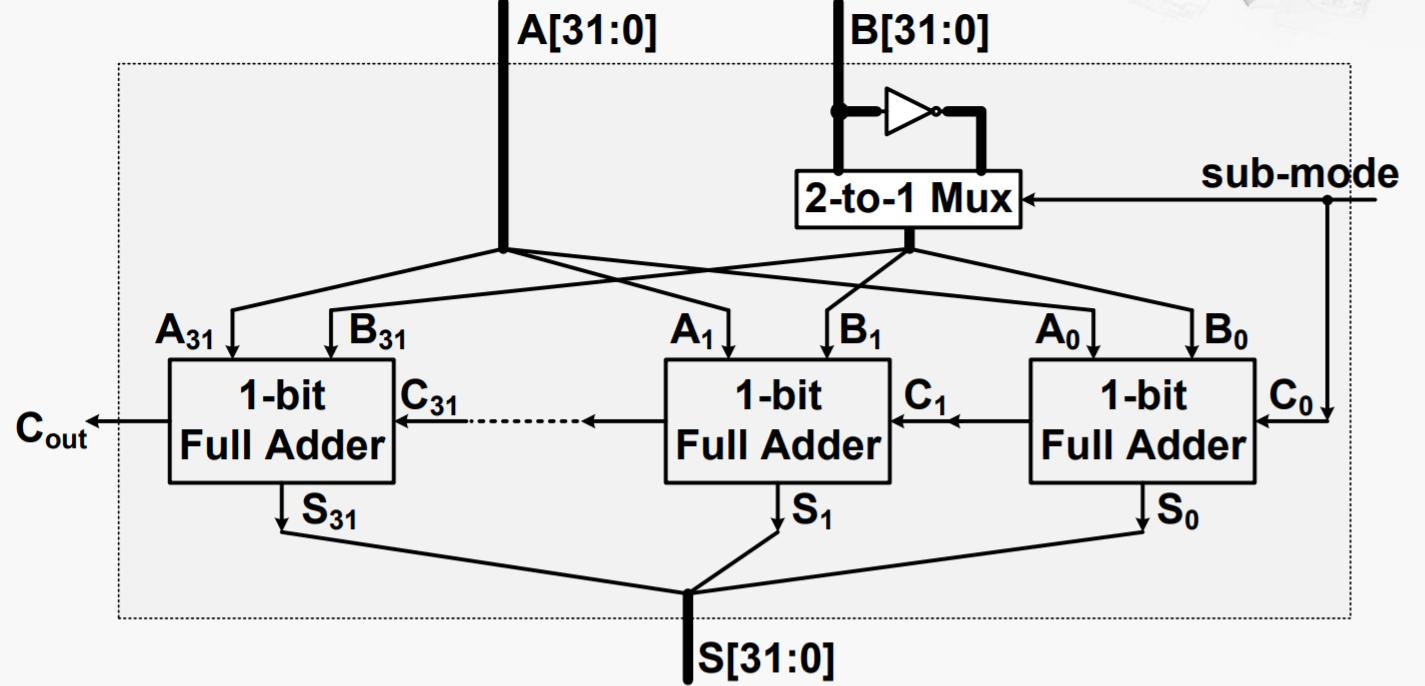

實現

這其實是一個加法和減法器,與之前的32-bit加法器相比,在輸入端B多了一個二選一多路選擇器,當sub-mode為0,是加法模式,也沒有來自低位的進位;當sub-mode為1時,是減法模式,首先B按位取反,同此同時sub-mode為是低位的進位,剛好是-B = ~B + 1.

參考連結:https://www.coursera.org/learn/jisuanji-zucheng/lecture/ydYAV/305-jia-fa-he-jian-fa-de-shi-xian