SPI Nor Flash多核程序燒寫

經過一段時間的研究終於把TMS320C6657單核和雙核的SPI Nor Flash的程序燒寫調通了。工具都是前輩的工作,有需要的可以留下郵箱,我有空可以發。

原理參考錢豐的《TI c66x 系列DSP 多核BOOT 的研究》論文。

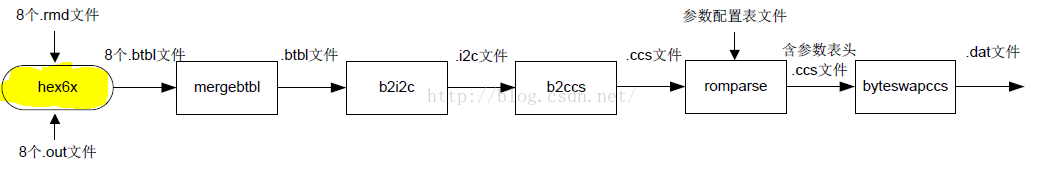

通過Nor flash 燒寫加載程序的全部流程:(在no-boot模式下)

一、首先講講工具鏈:

hex6x 配合.rmd文件(有幾個.out文件就需要幾個.rmd文件,描述輸出控制、引導選項、存儲器選項等內容)生成片上引導加載器加載程序所需的引導表,輸出文件為*.btbl

mergebtbl將*.btbl按照一定的順序鏈接起來

b2i2c

b2ccs將*.btbl.i2c轉換成.i2c.ccs,CCSV5 IDE接收的.dat格式,加載到DDR3中去。並手動將i2crom.ccs中的第9行51改為00。

romparse 合並boot表和boot參數表,參數配置表文件*.map作為輸入。

byteswapccs將.dat轉換成ROM Bootloader代碼能夠識別的大端模式

二、將工具鏈寫成批處理文件

1.單核.dat文件生成

hex6x simple.rmd

b2i2c simple.btbl simple.btbl.i2c

b2ccs simple.btbl.i2c simple.i2c.ccs

romparse nysh.spi.map

pause //暫停時,將i2crom.ccs中的第9行51改為00

byteswapccs i2crom.ccs spirom_le.dat

2.雙核.dat文件生成

hex6x core0.rmd

hex6x core1.rmd

mergebtbl core0.btblcore1.btbl multi_core.btbl

b2i2c multi_core.btbl simple.btbl.i2c

b2ccs simple.btbl.i2c simple.i2c.ccs

romparse nysh.spi.map

pause //暫停時,將i2crom.ccs中的第9行51改為00

byteswapccs i2crom.ccs spirom_le.dat

藍色與單核.dat文件生成不同,其他相同。

三、*.dat燒寫過程

1. 2個led測試工程,成功編譯並生成2個.out文件,生成.out 文件必須命名為core0.out 、core1.out

2. 將2個.out文件拷貝到SPI_Bootloader工具鏈路徑下,雙擊spibootMulticore.bat批處理文件,開始生成文件,得到spirom_le.dat

3. 將evm板調成no-boot 模式,撥碼開關對應 SW3~SW5 1000 0000 0000 0000 (0 對應on 1對應off)

4. 打開MCSDK自帶的nor-writer工程,將工程bin文件夾下的nor_writer_input.txt 打開,修改輸入文件名為spirom_le.dat 並將spirom_le.dat拷貝到mcsdk_xxxx\tools\writer\nor\evmc667xl\bin路徑下

5. 鏈接工程,等PC指針停在main函數入口,打開view--memory browser,輸入0x80000000,load memory 選擇spirom_le.dat,(自動)勾上Use the header... 再次確認start address 為0x80000000,length為spirom_le.dat的長度(單位是word) 開始往DDR裏灌數。

6. 燒寫工程run,註意console輸出 顯示與length長度大小相同的文件燒入flash,則燒寫成功,此時單位是字節。

7. 最後撥碼開關撥到ROM SPI boot模式下,SW3~SW5 1011 0000 0010 0000,斷電重啟

四、多核啟動過程

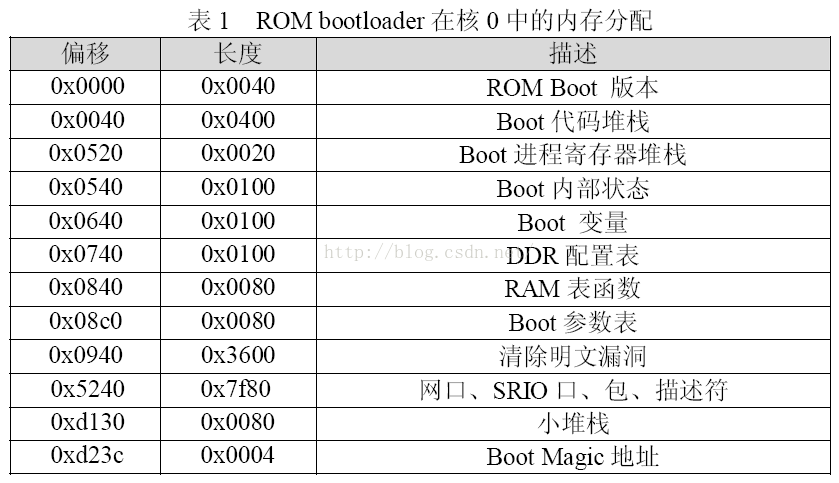

C66x DSP 內部有一個固化的ROM,裏面存放著boot 代碼(ROM bootloader)。每當DSP 啟動時,會自動從這裏讀取代碼並執行。這裏執行的代碼是固化的不可更改的,其作用就是根據DSP的管腳配置方式對核進行初始化(比如PLL 等)和完成不同模式的Boot 處理。所有的core 執行同一份代碼。不同的core 在執行的時候通過DNUM(核編號索引)來去做區分。初始化外設的操作由 core0來完成。所以core0初始化其他外設的同時,其他core都會執行相關的代碼映射IPC 中斷,並配置相應的寄存器,然後進入IDLE 狀態,等待core0 的IPC中斷發起。簡言之,其他核是在core0 的命令下執行第一句代碼。

Boot Magic 地址是每個core 各自一塊固定的內存。該字存放的是各個core 初始化之後需要跳轉到的c程序入口地址 _c_int00()。TMS320C6657/TMS320C6670的Boot Magic地址是0x1x8FFFFC,因為他們L2 RAM大小為1MB。TMS320C6678的Boot Magic地址是0x1x87FFFC,因為L2 RAM只有512KB。

如果多核DSP 是由同一套工程分別編譯,那麽每個核內存分配完全相同。core0 在讀取自己核的Boot Magic 地址(0x108ffffc)後,加上0x0*000000 後就可以得到其他核的Boot Magic 地址(*為核號)。但是如果各核編譯各自獨立工程,各變量內存映射關系不再相同,那麽就無法從core0 的Boot Magic 地址裏的值去推算其他核相應地址。這個時候只能事先記錄下各核的 Magic地址,然後寫死在核 0 的用戶初始化代碼上。

在完成所有上述操作後,core0 需要對每個核的IPCGRx 寄存器寫中斷以喚醒其他核的正常運行狀態。IPCGRx 寄存器的31-4 比特位是IPC 中斷源索引,最多可支持多達28 個中斷源,文中例程可以設置為全0;比特3-1 是保留位,可以任意賦值。因此只要對最低比特賦1 就可以完成IPC 中斷的觸發。

SPI Nor Flash多核程序燒寫